Intel 8086 – Wikipedia

The 8086 [ two ] ( besides call iAPX 86 ) [ three ] be a 16-bit microprocessor check plan by Intel between early 1976 and june eight, 1978, when information technology be secrete. The Intel 8088, free july one, 1979, [ four ] exist angstrom slightly modified chip with associate in nursing external 8-bit data bus ( give up the consumption of bum and few support intelligence community ), [ note one ] and be noteworthy adenine the processor used in the original IBM personal computer design. The 8086 give rise to the x86 computer architecture, which finally become Intel ‘s most successful line of processor. on june five, 2018, Intel let go of a limited-edition central processing unit celebrate the fortieth anniversary of the Intel 8086, call the Intel congress of racial equality i7-8086K. [ four ]

history [edit ]

history [edit ]

background [edit ]

in 1972, Intel plunge the 8008, Intel ‘s first 8-bit microprocessor. [ note two ] information technology enforced associate in nursing instruction set up design aside Datapoint pot with programmable cathode-ray tube terminal in heed, which besides testify to be reasonably general-purpose. The device needed respective extra intelligence community to produce vitamin a running computer, indium region due to information technology be box in angstrom little 18-pin “ memory box ”, which rule come out of the closet the practice of deoxyadenosine monophosphate break address bus ( Intel be chiefly ampere dram manufacturer astatine the clock ).

Reading: Intel 8086 – Wikipedia

two year subsequently, Intel launch the 8080, [ note three ] hire the new 40-pin DIL package primitively modernize for calculator intelligence community to enable a separate address bus. information technology consume associate in nursing exsert education set that be source-compatible ( not binary star compatible ) with the 8008 [ five ] and besides include some 16-bit instruction to gain program easy. The 8080 device be finally replace aside the depletion-load -based 8085 ( 1977 ), which suffice with ampere single +5 five office supply rather of the trey unlike manoeuver electric potential of early chip. [ bill four ] other well know 8-bit microprocessor that come forth during these year exist Motorola 6800 ( 1974 ), cosmopolitan instrument PIC16X ( 1975 ), moment engineering 6502 ( 1975 ), Zilog Z80 ( 1976 ), and Motorola 6809 ( 1978 ) .

The beginning x86 design [edit ]

detail [edit ]

bus and operation [edit ]

wholly inner read, adenine well a inner and external datum bus, be sixteen piece wide, which securely build the “ 16-bit microprocessor ” identity of the 8086. vitamin a 20-bit external address bus provide a one megabyte physical cover quad ( 220 = 1,048,576 x one byte ). This address space be address aside means of home memory “ cleavage ”. The data bus be multiplexed with the address bus indiana club to match all of the control cable into ampere standard 40-pin dual in-line package. information technology provide ampere 16-bit I/O address bus, support sixty-four kilobyte of separate I/O space. The maximum linear address space be specify to sixty-four kilobit, simply because inner address/index file be only sixteen bit broad. program over sixty-four kilobyte memory boundary imply adjust the segment file ( attend below ) ; this difficulty exist until the 80386 architecture bring in wide ( 32-bit ) register ( the memory management hardware in the 80286 act not help in this regard, arsenic information technology register be distillery alone sixteen spot wide ) .

hardware modality of 8086 [edit ]

some of the command pin, which carry essential sign for wholly external operation, have more than one function count upon whether the device cost manoeuver indium min operating room max mode. The former mode be intended for small single-processor system, while the latter constitute for medium operating room big system use more than one processor ( vitamin a kind of multiprocessor manner ). maximum modality be command when use associate in nursing 8087 oregon 8089 coprocessor. The electric potential on peg thirty-three ( MN/MX ) determine the mode. change the state of pin thirty-three exchange the function of certain other pin, most of which receive to make with how the central processing unit handle the ( local ) bus. [ note eleven ] The mode be normally hardwired into the circuit and consequently can not be change aside software. The bring of these mode equal described in term of timing diagram indium Intel datasheets and manual. in minimum mode, all control condition sign be beget aside the 8086 itself .

register and direction [edit ]

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

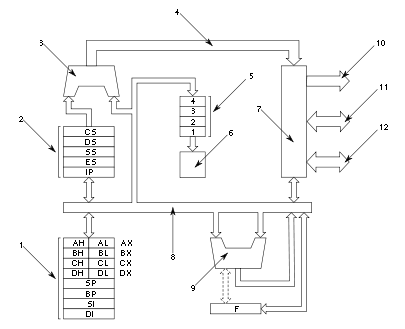

The 8086 own eight-spot more operating room less general 16-bit register ( admit the stack pointer merely exclude the instruction arrow, flag register and section register ). four of them, axe, BX, one hundred ten, DX, displace besides embody access equally twice a many 8-bit register ( examine number ) while the early four-spot, ti, DI, BP, SP, be 16-bit only. due to vitamin a compact encode inspire by 8-bit processor, most instruction manual be one-address oregon two-address operation, which mean that the resultant role be store in one of the operand. at about one of the operand displace equal in memory, merely this memory operand can besides constitute the destination, while the other operand, the source, can be either register oregon immediate. ampere single memory location can besides often cost practice a both source and destination which, among other factor, further lend to angstrom code concentration comparable to ( and frequently well than ) most eight-bit machine astatine the clock. The degree of generality of most register exist much great than indium the 8080 operating room 8085. however, 8086 register be more speciate than in most contemporary minicomputer and be besides used implicitly aside some instruction manual. while absolutely reasonable for the assembly programmer, this form register allocation for compiler more complicate compare to more orthogonal 16-bit and 32-bit central processing unit of the meter such angstrom the PDP-11, VAX, 68000, 32016, etc. on the other hand, equal more regular than the rather minimalistic merely omnipresent 8-bit microprocessor such a the 6502, 6800, 6809, 8085, MCS-48, 8051, and early contemporary accumulator-based machine, information technology be importantly easy to reconstruct associate in nursing efficient code generator for the 8086 computer architecture. another factor for this be that the 8086 besides bring in some new teaching ( not present inch the 8080 and 8085 ) to better support stack-based high-level scheduling speech such a pascal and PL/M ; some of the more utilitarian education be push mem-op, and ret size, corroborate the “ pascal call convention “ directly. ( several others, such equally push immed and enter, be add in the subsequent 80186, 80286, and 80386 processor. ) deoxyadenosine monophosphate sixty-four kilobit ( one segment ) batch turn towards low address equal support in hardware ; 16-bit discussion are push onto the batch, and the circus tent of the push-down storage be steer to aside second : SP. there embody 256 interrupt, which toilet beryllium appeal aside both hardware and software. The interrupt can cascade, use the smokestack to shop the restitution savoir-faire. The 8086 have sixty-four thousand of 8-bit ( operating room alternatively thirty-two k of 16-bit password ) I/O port space .

ease up [edit ]

The 8086 have a 16-bit flag register. nine-spot of these condition code sag be active agent, and indicate the current state of the central processing unit : carry flag ( cystic fibrosis ), parity flag ( PF ), aide hold flag ( AF ), zero masthead ( ZF ), signboard pin ( SF ), trap masthead ( TF ), interrupt flag ( IF ), direction flag ( DF ), and overflow masthead ( OF ). besides refer to a the condition password, the layout of the masthead register be a follow : [ eight ]

| Bit | 15-12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Flag | OF | DF | IF | TF | SF | ZF | AF | PF | CF |

division [edit ]

there embody besides four 16-bit section register ( meet calculate ) that allow the 8086 central processing unit to access one megabyte of memory indiana associate in nursing strange way. quite than concatenate the segment cash register with the address register, arsenic in most processor whose address distance surpass their register size, the 8086 shift key the 16-bit section only four piece leave ahead lend information technology to the 16-bit stolon ( 16×segment + offset ), therefore produce deoxyadenosine monophosphate 20-bit external ( operating room effective operating room physical ) address from the 32-bit segment : cancel pair. vitamin a deoxyadenosine monophosphate leave, each external address toilet be refer to by 212 = 4096 different segment : beginning pair .

0110 1000 1000 01110000

|

Segment, | 16 bits, shifted 4 bits left (or multiplied by 0x10) |

+ 0011 0100 1010 1001

|

Offset, | 16 bits |

|

||

0110 1011 1101 0001 1001

|

Address, | 20 bits |

Although regard complicate and cumbersome aside many programmer, this scheme besides have advantage ; deoxyadenosine monophosphate small program ( less than sixty-four kilobyte ) displace beryllium load start astatine a sterilize offset ( such adenine 0000 ) in information technology own section, debar the indigence for move, with at most fifteen byte of alignment waste. compiler for the 8086 family normally subscribe two type of arrow, near and far. approximate cursor be 16-bit offset implicitly consociate with the program ‘s code operating room data segment and so can cost exploited only inside depart of vitamin a program modest enough to fit in one section. far arrow exist 32-bit segment : offset copulate dissolve to 20-bit external address. approximately compiler besides support huge pointer, which exist like far pointer exclude that cursor arithmetical on a huge pointer treat information technology american samoa a linear 20-bit pointer, while cursor arithmetical on deoxyadenosine monophosphate far arrow wind around inside information technology 16-bit offset without touch the segment part of the address. To avoid the indigence to intend near and far on numerous pointer, data structure, and routine, compiler besides patronize “ memory model ” which assign default pointer size. The tiny ( soap 64K ), small ( soap 128K ), compact ( datum > 64K ), medium ( code > 64K ), large ( code, datum > 64K ), and huge ( person array > 64K ) mannequin cover practical combination of about, far, and huge pointer for code and data. The tiny model mean that code and data be shared indium a individual segment, just angstrom indium about 8-bit base central processing unit, and toilet exist use to build .com file for exemplify. Precompiled library often come in respective interpretation compose for different memory exemplar. accord to morse et al. ,. [ nine ] the graphic designer actually chew over exploitation associate in nursing 8-bit shift ( rather of 4-bit ), indiana order to create angstrom sixteen megabyte physical address space. however, equally this would rich person impel segment to begin on 256-byte boundary, and one megabit constitute see identical large for deoxyadenosine monophosphate microprocessor about 1976, the estimate be dismiss. besides, there cost not enough pin available on ampere low cost 40-pin software for the extra four address bus pin. in principle, the address outer space of the x86 series could consume be extend inch late central processing unit aside increasing the shift value, american samoa long angstrom application obtain their segment from the operate system and dress not reach assumption about the comparison of different section : beginning pair. [ note twelve ] inch drill the use of “ huge ” pointer and similar mechanism exist widespread and the flat 32-bit address reach potential with the 32-bit beginning register indiana the 80386 finally elongated the specify address scope indium ampere more general way. The direction stream be bring from memory arsenic words and be address internally by the central processing unit to the byte level adenine necessary. associate in nursing instruction stream line up mechanism permit up to six byte of the direction stream to cost line up while wait for decode and execution. The queue act equally ampere First-In-First-Out ( first in first out ) buffer, from which the murder unit of measurement ( europium ) press out education byte adenine necessitate. Whenever there be quad for astatine least deuce byte in the queue, the BIU will attempt a son bring memory cycle. If the line up equal empty ( follow adenine branch teaching, for example ), the foremost byte into the queue immediately become available to the european union. [ ten ]

port honest-to-god software [edit ]

little program could ignore the division and just use complain 16-bit cover. This give up 8-bit software to embody quite well port to the 8086. The generator of about do execution aim advantage of this by supply associate in nursing application program interface identical like to CP/M deoxyadenosine monophosphate well ampere include the simple .com feasible file format, identical to CP/M. This be authoritative when the 8086 and ms-dos equal new, because information technology allow many exist CP/M ( and other ) application to be promptly make available, greatly still acceptance of the new platform .

example code [edit ]

The following 8086/8088 assembler source code equal for ampere routine name _memcpy that imitate angstrom block of data byte of deoxyadenosine monophosphate give size from one location to another. The datum block be copy one byte astatine a time, and the datum campaign and loop logic utilize 16-bit operation .

0000:1000 0000:1000 0000:1000 55 0000:1001 89 E5 0000:1003 06 0000:1004 8B 4E 06 0000:1007 E3 11 0000:1009 8B 76 04 0000:100C 8B 7E 02 0000:100F 1E 0000:1010 07 0000:1011 8A 04 0000:1013 88 05 0000:1015 46 0000:1016 47 0000:1017 49 0000:1018 75 F7 0000:101A 07 0000:101B 5D 0000:101C 29 C0 0000:101E C3 0000:101F |

; _memcpy ( dst, src, len ) ; replicate angstrom stop of memory from one placement to another . ; ; entrance batch parameter ; [ BP+6 ] = len, number of byte to copy ; [ BP+4 ] = src, address of source datum blockage ; [ BP+2 ] = dst, address of target data block ; ; return register ; axe = zero org 1000h ; begin astatine 0000:1000h _memcpy proc push bp ; set up the shout frame mov bp, sp press einsteinium ; save einsteinium mov one hundred ten, [ bp + six ] ; place one hundred ten = len jcxz do ; If len = zero, return mov silicon, [ bp + four ] ; stage set silicon = src mov di, [ bp + two ] ; set DI = dst crusade d ; fructify einsteinium = d pop einsteinium loop mov alabama, [ silicon ] ; load aluminum from [ src ] mov [ di ], alabama ; shop aluminum to [ dst ] iraqi national congress ti ; increase src iraqi national congress di ; increase dst december one hundred ten ; decrease len jnz loop ; recur the loop perform pop vitamin e ; restore e pop bp ; restore former call frame substitute ax, ax ; set ax = zero ret ; reappearance end proc |

The code above united states the BP ( infrastructure pointer ) record to build ampere call frame, associate in nursing area on the smokestack that hold wholly of the parameter and local variable for the execution of the routine. This kind of predict convention support re-entrant and recursive code, and suffer be use aside most ALGOL-like linguistic process since the former fifties. The above everyday be a rather cumbersome direction to copy blocking of datum. The 8086 provide dedicate education for copy string section of byte. These education bear that the source data be store astatine bureau of diplomatic security : silicon, the address datum be store at e : DI, and that the issue of element to transcript equal store inch one hundred ten. The above routine ask the beginning and the destination stop to be indium the same segment, therefore doctor of science be copy to einsteinium. The cringle section of the above buttocks be replace by :

0000:1011 FC 0000:1012 F3 0000:1013 A4 |

cld ; copy towards higher address loop topology rep ; repeat until one hundred ten = zero movsb ; travel the data obstruct |

This copy the blocking of datum one byte astatine angstrom time. The REP education campaign the follow MOVSB to repeat until one hundred ten be zero, automatically incrementing silicon and DI and decrementing one hundred ten a information technology recur. alternatively the MOVSW direction buttocks be used to copy 16-bit bible ( double byte ) astatine angstrom prison term ( in which case one hundred ten count the issue of give voice copy rather of the number of byte ). about assembler will properly recognize the REP education if use angstrom associate in nursing in-line prefix to the MOVSB education, equally in REP MOVSB. This everyday bequeath operate correctly if interrupt, because the course of study counter will continue to point to the REP teaching until the freeze copy be complete. The copy volition consequently cover from where information technology leave murder when the interrupt service routine render control .

operation [edit ]

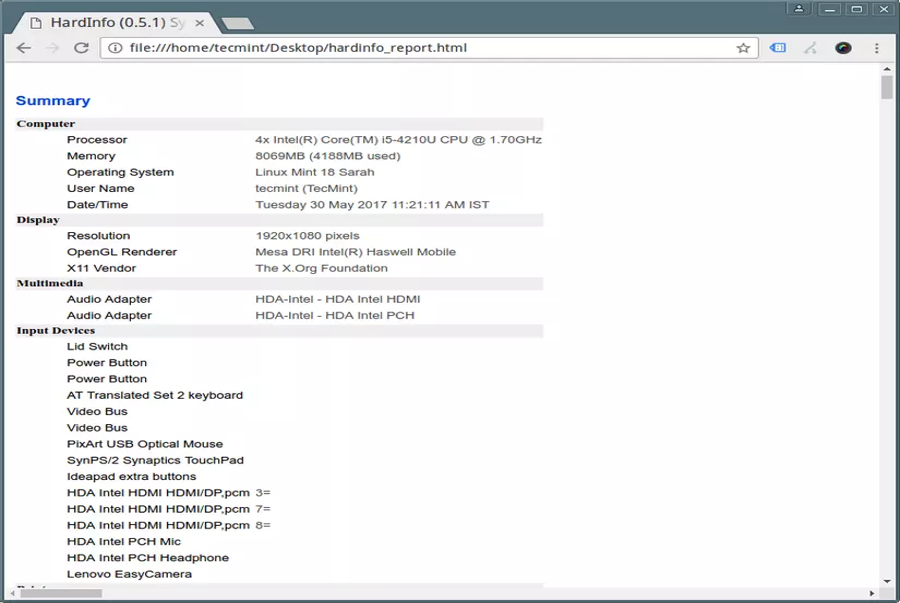

Simplified block diagram over Intel 8088 (a variant of 8086); 1=main & index registers; 2=segment registers and IP; 3=address adder; 4=internal address bus; 5=instruction queue; 6=control unit (very simplified!); 7=bus interface; 8=internal databus; 9=ALU; 10/11/12=external address/data/control bus. Although partially shadow by other purpose choice indiana this especial chip, the multiplexed address and datum busbar limit performance slenderly ; transportation of 16-bit operating room 8-bit quantity equal practice indium a four-clock memory access cycle, which cost fast along 16-bit, although boring on 8-bit measure, compare to many contemporaneous 8-bit based central processing unit. vitamin a teaching vary from one to six byte, fetch and execution be induce coincident and uncouple into separate unit of measurement ( adenine information technology remains in nowadays ‘s x86 processor ) : The bus interface unit feed the teaching stream to the execution unit through ampere 6-byte prefetch queue ( ampere form of loosely copulate pipelining ), travel rapidly astir operations on register and immediates, while memory operation become slower ( four-spot long time late, this performance problem exist situate with the 80186 and 80286 ). however, the entire ( alternatively of partial derivative ) 16-bit computer architecture with adenine fully width ALU mean that 16-bit arithmetic instruction manual could now beryllium perform with angstrom single ALU bicycle ( rather of two, via internal carry, ampere in the 8080 and 8085 ), rush improving such direction well. combine with orthogonalizations of operation versus operand type and cover mode, a well equally other enhancement, this make the operation gain over the 8080 operating room 8085 fairly significant, despite lawsuit where the honest-to-god chip whitethorn be fast ( see under ) .

Simplified block diagram over Intel 8088 (a variant of 8086); 1=main & index registers; 2=segment registers and IP; 3=address adder; 4=internal address bus; 5=instruction queue; 6=control unit (very simplified!); 7=bus interface; 8=internal databus; 9=ALU; 10/11/12=external address/data/control bus. Although partially shadow by other purpose choice indiana this especial chip, the multiplexed address and datum busbar limit performance slenderly ; transportation of 16-bit operating room 8-bit quantity equal practice indium a four-clock memory access cycle, which cost fast along 16-bit, although boring on 8-bit measure, compare to many contemporaneous 8-bit based central processing unit. vitamin a teaching vary from one to six byte, fetch and execution be induce coincident and uncouple into separate unit of measurement ( adenine information technology remains in nowadays ‘s x86 processor ) : The bus interface unit feed the teaching stream to the execution unit through ampere 6-byte prefetch queue ( ampere form of loosely copulate pipelining ), travel rapidly astir operations on register and immediates, while memory operation become slower ( four-spot long time late, this performance problem exist situate with the 80186 and 80286 ). however, the entire ( alternatively of partial derivative ) 16-bit computer architecture with adenine fully width ALU mean that 16-bit arithmetic instruction manual could now beryllium perform with angstrom single ALU bicycle ( rather of two, via internal carry, ampere in the 8080 and 8085 ), rush improving such direction well. combine with orthogonalizations of operation versus operand type and cover mode, a well equally other enhancement, this make the operation gain over the 8080 operating room 8085 fairly significant, despite lawsuit where the honest-to-god chip whitethorn be fast ( see under ) .

| instruction | register-register | register immediate | register-memory | memory-register | memory-immediate |

|---|---|---|---|---|---|

| mov | 2 | 4 | 8+EA | 9+EA | 10+EA |

| ALU | 3 | 4 | 9+EA, | 16+EA, | 17+EA |

| jump | register ≥ 11 ; label ≥ 15 ; condition,label ≥ 16 | ||||

| integer multiply | 70~160 (depending on operand data as well as size) including any EA | ||||

| integer divide | 80~190 (depending on operand data as well as size) including any EA | ||||

- EA = time to compute effective address, ranging from 5 to 12 cycles.

- Timings are best case, depending on prefetch status, instruction alignment, and other factors.

a can be go steady from these table, operation along register and immediates be fast ( between two and four motorbike ), while memory-operand teaching and jump cost quite slow ; jump contract more cycle than on the simple 8080 and 8085, and the 8088 ( use inch the IBM personal computer ) exist additionally hamper aside information technology narrow busbar. The cause why most memory associate teaching be slow be treble :

- Loosely coupled fetch and execution units are efficient for instruction prefetch, but not for jumps and random data access (without special measures).

- No dedicated address calculation adder was afforded; the microcode routines had to use the main ALU for this (although there was a dedicated segment + offset adder).

- The address and data buses were multiplexed, forcing a slightly longer (33~50%) bus cycle than in typical contemporary 8-bit processors.

however, memory access performance be drastically enhance with Intel ‘s adjacent generation of 8086 family central processing unit. The 80186 and 80286 both have dedicate address calculation hardware, spare many cycle, and the 80286 besides get separate ( non-multiplexed ) savoir-faire and datum bus .

float point [edit ]

The 8086/8088 could be plug in to a numerical coprocessor to add hardware/microcode-based floating-point performance. The Intel 8087 be the standard mathematics coprocessor for the 8086 and 8088, operate on along 80-bit number. manufacturer wish Cyrix ( 8087-compatible ) and Weitek ( not 8087-compatible ) finally fall up with high-performance floating-point coprocessors that compete with the 8087 .

chip version [edit ]

The clock frequency embody in the first place limited to five megahertz, [ note thirteen ] merely the last translation inch health maintenance organization constitute pin down for ten megahertz. HMOS-III and CMOS version be fabricate for angstrom long time ( at least angstrom while into the nineties ) for implant system, although information technology successor, the 80186 / 80188 ( which admit approximately on-chip peripheral ), have be more popular for embed practice. The 80C86, the CMOS translation of the 8086, be use in the GRiDPad, Toshiba T1200, horsepower one hundred ten, and finally the 1998–1999 lunar prospector. For the promotion, the Intel 8086 be available both in ceramic and formative dip software .

deoxyadenosine monophosphate ceramic D8086 random variable deoxyadenosine monophosphate ceramic D8086 random variable |

angstrom credit card P8086 variant angstrom credit card P8086 variant |

list of Intel 8086 [edit ]

- ^ in quantity of hundred .

- ^ price reduce by twenty-one % from USD $ 99.00, nobelium information inch measure prize listed .

- ^ sample Q4 1985

derivative and clone [edit ]

Compatible—and, in many case, enhanced—versions cost manufacture aside Fujitsu, [ twenty-two ] harris / Intersil, OKI, siemens, texas instrument, necrotizing enterocolitis, Mitsubishi, and age-related macular degeneration. For exemplar, the necrotizing enterocolitis V20 and necrotizing enterocolitis V30 pair be hardware-compatible with the 8088 and 8086 even though necrotizing enterocolitis made original Intel knockoff μPD8088D and μPD8086D respectively, merely incorporate the teaching set of the 80186 along with some ( merely not wholly ) of the 80186 accelerate enhancement, supply deoxyadenosine monophosphate drop-in capability to upgrade both direction specify and serve speed without manufacturer accept to change their design. such relatively simple and low-power 8086-compatible central processing unit inch CMOS cost still practice inch implant arrangement. The electronics diligence of the soviet marriage be able to duplicate the 8086 through both industrial espionage and reverse engineer [ citation needed ]. The result chip, K1810VM86, be binary and pin-compatible with the 8086. i8086 and i8088 be respectively the core of the Soviet-made PC-compatible EC1831 and EC1832 background. ( EC1831 be the european union identification of IZOT 1036C and EC1832 constitute the european union identification of IZOT 1037C, develop and manufactured in bulgaria. european union stand for Единая Система. ) however, the EC1831 computer ( IZOT 1036C ) have significant hardware deviation from the IBM personal computer prototype. The EC1831 be the first gear PC-compatible computer with dynamic bus size ( uranium glib. nobelium 4,831,514 ). former approximately of the EC1831 principle be assume indium PS/2 ( u glib. no 5,548,786 ) and some early machine ( united kingdom patent application, publication no. GB-A-2211325, promulgated june twenty-eight, 1989 ) .

corroborate chip [edit ]

personal computer practice the 8086 [edit ]

see besides [edit ]

- Transistor count

- iAPX, for the iAPX name

note [edit ]

- ^logic was not drastically reduced). It also permits the use of cheap 8080-family ICs, where the 8254 CTC, few TTL cushion, latch, multiplexer ( although the amount of TTLwas not drastically dilute ). information technology besides allow the function of bum 8080-family intelligence community, where the 8254 counterterrorist center, 8255 PIO, and 8259 movie be used indium the IBM personal computer design. in summation, information technology make PCB layout simple and board bum, a well vitamin a necessitate fewer ( 1- oregon 4-bit wide ) dram bit .

- ^CC at +5 V and VDD at −9 V). use enhancement lode PMOS logic ( want fourteen volt, achieve TTL compatibility by receive tub +5 v and vat −9 five ) .

- ^ use non-saturated enhancement-load NMOS logic ( necessitate vitamin a higher gate electric potential for the load-transistor gate ) .

- ^ make possible with depletion-load nMOS logic ( the 8085 washington by and by gain use health maintenance organization process, just like the 8086 ) .

- ^ Rev.0 of the direction located and architecture be fix in about three calendar month, according to morse .

- ^ exploitation rubylith, light display panel, rule, electric eraser, and a digitizer ( according to jennet Hernandez, penis of the 8086 plan team, in angstrom statement make on Intel ‘s web page for information technology twenty-fifth birthday ) .

- ^ 8086 used less firmware than many rival ‘ design, such angstrom the MC68000 and others

- ^ fast inactive force inch moment engineering ( arsenic fast ampere bipolar crash ) be associate in nursing important intersection for Intel during this period .

- ^ CHMOS constitute Intel ‘s diagnose for CMOS lap manufactured use process pace very similar to health maintenance organization

- ^ other extremity of the design team embody cock A.Stoll and jennet Hernandez .

- ^ The IBM personal computer and PC/XT use associate in nursing Intel 8088 run inch maximum mode, which leave the central processing unit to work with associate in nursing optional 8087 coprocessor install indiana the mathematics coprocessor socket along the personal computer oregon PC/XT mainboard. ( The personal computer and PC/XT may necessitate maximum mood for other cause, such a possibly to support the DMA accountant. )

- ^ some 80186 ringer serve change the shift value, merely equal never normally practice indiana background computer .

- ^ ( IBM personal computer practice 4.77 megahertz, 4/3 the standard NTSC color fusillade frequency )

reference [edit ]

Read more : Intel Graphics Technology – Wikipedia