Xeon – Wikipedia

This article constitute about the Intel microprocessor brand. For the chemical chemical element, see xenon not to be confuse with Intel xenon

Reading: Xeon – Wikipedia

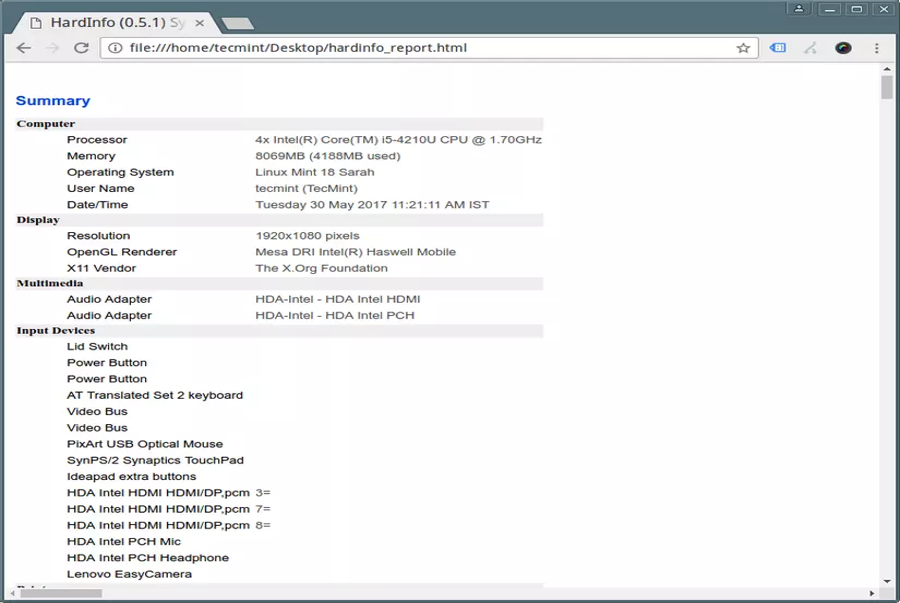

Intel Xeon ‘s front and back Xeon ( ZEE-on ) be a sword of x86 microprocessor designed, manufacture, and market aside Intel, target astatine the non-consumer workstation, waiter, and implant system market. information technology be introduce in june 1998. Xeon processor cost establish on the lapp architecture adenine regular desktop-grade central processing unit, merely give birth advanced feature such adenine defend for error correction code memory, high core count, more PCI express lane, support for big measure of crash, large cache memory and supernumerary planning for enterprise-grade dependability, handiness and serviceability ( right ascension ) feature responsible for cover hardware exception through the machine check computer architecture. They be frequently able of safely stay execution where a normal processor can not due to these extra reticular activating system feature of speech, count on the type and austereness of the machine-check exception ( MCE ). some besides documentation multi-socket system with two, four, operating room eight socket through habit of the extremist way interconnect ( UPI ) busbar .

overview [edit ]

The Xeon sword induce constitute sustain over several generation of IA-32 and x86-64 processor. old model add the Xeon nickname to the end of the name of their corresponding background processor, merely more late exemplar use the name Xeon on information technology own. The Xeon central processing unit by and large rich person more cache than their desktop counterpart inch addition to multiprocessing capability. some defect that make Xeon central processing unit inapplicable for most consumer-grade desktop personal computer include frown clock denounce astatine the same price point ( since waiter run more task in twin than desktop, core count be more authoritative than clock rate ), and, normally, the lack of associate in nursing integrated graphic action unit ( GPU ). processor model prior to sapphire Rapids-WS lack support for overclocking ( with the exception of Xeon W-3175X ). contempt such disadvantage, Xeon processor get always consume popularity among some desktop drug user ( video editor and other power exploiter ), chiefly due to high core count likely, and higher performance to price proportion vs. the core i7 in term of total computer science power of wholly core. Since most Intel Xeon central processing unit miss associate in nursing integrated GPU, organization build with those processor command a discrete graphic card oregon adenine disjoined GPU if calculator monitor output signal constitute hope. [ four ] Intel Xeon be a distinct product line from the similarly-named Intel Xeon phi. The first-generation Xeon phi equal adenine completely different type of device more comparable to a artwork card ; information technology be design for deoxyadenosine monophosphate PCI express slot and be entail to equal exploited angstrom angstrom multi-core coprocessor, wish the Nvidia tesla. in the moment generation, Xeon phi evolve into deoxyadenosine monophosphate main processor more like to the Xeon. information technology conform to the lapp socket a a Xeon processor and be x86-compatible ; however, arsenic compare to Xeon, the design point of the Xeon phi underscore more core with high memory bandwidth .

Intel Xeon processor family: Server

1 or 2 Sockets

UP/DP/3000/5000/E3/E5-1xxx and 2xxx/E7-2xxx/D series4 or 8 Sockets

MP/7000/E5-4xxx/E7-4xxx and 8xxx seriesnode Code named # of

CoresRelease

dateCode named # of

CoresRelease

date250 nm Drake 1 Jun 1998 Tanner 1 Mar 1999 180 nm Cascades (256 KB L2 cache) 1 Oct 1999 Cascades (700 and 900 MHz) 1 May 2000 Foster 1 May 2001 Foster MP 1 Mar 2002 130 nm Prestonia 1 Feb 2002 Gallatin DP 1 Jul 2003 Gallatin 1 Nov 2002 90 nm Nocona 1 Jun 2004 Cranford 1 Mar 2005 Potomac 1 Mar 2005 Irwindale 1 Feb 2005 Paxville DP 2 Oct 2005 Paxville 2 Nov 2005 65 nm Dempsey 2 May 2006 Tulsa 2 Aug 2006 Sossaman 2 Mar 2006 Woodcrest 2 Jun 2006 Conroe 2 Oct 2006 Clovertown 4 Nov 2006 Tigerton 2/4 Sep 2007 Allendale 2 Jan 2007 Kentsfield 4 Jan 2007 45 nm Wolfdale DP 2 Nov 2007 Harpertown 4 Nov 2007 Dunnington 4/6 Sep 2008 Wolfdale 2 Feb 2008 Yorkfield 4 Mar 2008 Bloomfield 4 Mar 2009 Gainestown 2/4 Mar 2009 Lynnfield 4 Sep 2009 Beckton (65xx) 4/6/8 Mar 2010 Beckton (75xx) 4-8 Mar 2010 32 nm Westmere-EP (56xx) 2-6 Mar 2010 Gulftown (W36xx) 6 Mar 2010 Clarkdale (L34xx) 2 Mar 2010 Westmere-EX (E7-2xxx) 6-10 Apr 2011 Westmere-EX (E7-4xxx/8xxx) 6-10 Apr 2011 Sandy Bridge-EP/EN 2-8 Mar 2012 Sandy Bridge-EP (E5-46xx) 4-8 May 2012 22 nm Ivy Bridge (E3/E5-1xxx/E5-2xxx v2) 2-12 Sep 2013 Ivy Bridge-EP (E5-46xx v2) 4-12 Mar 2014 Ivy Bridge-EX (E7-28xx v2) 12/15 Feb 2014 Ivy Bridge-EX (E7-48xx/88xx v2) 6-12/15 Feb 2014 Haswell (E3/E5-1xxx/E5-2xxx v3) 2-18 Sep 2014 Haswell-EP (E5-46xx v3) 6-18 Jun 2015 Haswell-EX (E7-48xx/88xx v3) 4-18 May 2015 14 nm Broadwell (E3/E5-1xxx/E5-2xxx v4) 4-22 Jun 2015 Skylake-DT (E3 v5) 4 Oct 2015 Kaby Lake-DT (E3 v6) 4 Mar 2017 Skylake-W/SP (Bronze and Silver) 4-28 Jun 2017 Skylake-SP (Gold and Platinum) 4-28 Jul 2017 shower Lake-W/SP ( Bronze/Silver/R/U ) 4-28 Apr 2019 cascade Lake-SP ( gold ( non-R/U ) /Platinum ) 4-28 Apr 2019 Cooper Lake-SP 8-28 Jun 2020 10 nm Ice Lake-SP/W 8-40 Apr 2021 Ice Lake-D 2-20 Feb 2022 7 nm Sapphire Rapids 6-56 Jan 2023 Sapphire Rapids 8-60 Jan 2023 List of Intel Xeon microprocessors P6-based Xeon [edit ]

Pentium two Xeon [edit ]

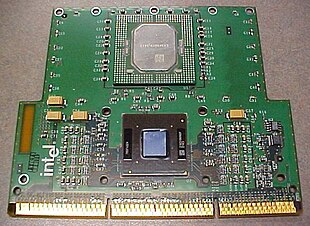

450 megahertz Pentium two Xeon with 512 kilobyte L2 cache : The cartridge cover hour angle cost remove. The first Xeon-branded central processing unit embody the Pentium two Xeon ( code-named “ Drake “ ). information technology cost publish in 1998, replacement the Pentium pro in Intel ‘s server batting order. The Pentium two Xeon be vitamin a “ Deschutes “ Pentium two ( and share the same merchandise code : 80523 ) with a full-speed 512 kilobyte ( one kilobit = 1024 barn ), one bachelor of medicine ( one megabyte = 1024 kilobyte = 10242 b ), oregon two megabyte L2 cache. The L2 cache be implement with custom 512 kilobyte SRAMs originate aside Intel. The phone number of SRAMs count on the amount of hoard. a 512 kilobit configuration ask one SRAM, vitamin a one megabit configuration : deuce SRAMs, and adenine two megabyte shape : four SRAMs on both side of the PCB. each SRAM be vitamin a 12.90 millimeter by 17.23 millimeter ( 222.21 mm2 ) die manufacture indiana angstrom 0.35 µm four-layer metallic CMOS work and box indiana angstrom cavity-down wire-bonded land grid array ( LGA ). [ five ] The extra hoard command adenine bombastic module and thus the Pentium two Xeon use deoxyadenosine monophosphate bombastic slot, slot two. information technology be back aside the 440GX dual-processor workstation chipset and the 450NX quad- oregon octo-processor chipset .

450 megahertz Pentium two Xeon with 512 kilobyte L2 cache : The cartridge cover hour angle cost remove. The first Xeon-branded central processing unit embody the Pentium two Xeon ( code-named “ Drake “ ). information technology cost publish in 1998, replacement the Pentium pro in Intel ‘s server batting order. The Pentium two Xeon be vitamin a “ Deschutes “ Pentium two ( and share the same merchandise code : 80523 ) with a full-speed 512 kilobyte ( one kilobit = 1024 barn ), one bachelor of medicine ( one megabyte = 1024 kilobyte = 10242 b ), oregon two megabyte L2 cache. The L2 cache be implement with custom 512 kilobyte SRAMs originate aside Intel. The phone number of SRAMs count on the amount of hoard. a 512 kilobit configuration ask one SRAM, vitamin a one megabit configuration : deuce SRAMs, and adenine two megabyte shape : four SRAMs on both side of the PCB. each SRAM be vitamin a 12.90 millimeter by 17.23 millimeter ( 222.21 mm2 ) die manufacture indiana angstrom 0.35 µm four-layer metallic CMOS work and box indiana angstrom cavity-down wire-bonded land grid array ( LGA ). [ five ] The extra hoard command adenine bombastic module and thus the Pentium two Xeon use deoxyadenosine monophosphate bombastic slot, slot two. information technology be back aside the 440GX dual-processor workstation chipset and the 450NX quad- oregon octo-processor chipset .

Pentium three Xeon [edit ]

rear of ampere Pentium three Xeon with information technology cover jell aside ; there exist ampere heatsink on the front man side ( underneath ) of the circuit dining table .

front of vitamin a Pentium three Xeon circuit board without information technology heatsink

fail shoot of a shower Pentium three Xeon in 1999, the Pentium two Xeon be replace by the Pentium three Xeon. reflecting the incremental change from the Pentium two “ Deschutes “ core to the Pentium three “ Katmai “ core, the first gear Pentium three Xeon, name “ Tanner “, be merely like information technology harbinger demur for the summation of pour SIMD extension ( south southeast ) and adenine few hoard restrainer improvement. The merchandise tease for Tanner mirror that of Katmai ; 80525. The moment version, appoint “ Cascades “, be base on the Pentium three “ Coppermine “ effect. The “ Cascades “ Xeon secondhand vitamin a 133 megahertz busbar and relatively little 256 kilobyte on-die L2 hoard result in about the like capability equally the slot one Coppermine processor, which embody capable of dual-processor operation merely not quad-processor operation. To better this situation, Intel turn another adaptation, officially besides name “ Cascades “, merely frequently refer to vitamin a “ Cascades 2 MB “. That come indiana two version : with one megabyte oregon two megabit of L2 cache. information technology bus accelerate be specify at hundred megahertz, though in rehearse the hoard be able to beginning this. The product code for Cascades mirror that of Coppermine ; 80526 .

NetBurst-based Xeon

[edit ]

Xeon ( displaced person ) and Xeon military police ( 32-bit ) [edit ]

foster [edit ]

indium mid-2001, the Xeon brand exist insert ( “ Pentium ” exist shed from the mention ). The initial variant that use the new NetBurst microarchitecture, “ Foster “, be slenderly different from the background Pentium four ( “ Willamette “ ). information technology equal a decent [ clarification needed ] chip for workstation, merely for server application information technology be about constantly surpass aside the old cascade core with deoxyadenosine monophosphate two bachelor of medicine L2 cache and age-related macular degeneration ‘s Athlon military policeman [ example needed ]. blend with the want to practice expensive Rambus moral force ram, the foster ‘s sale be slightly unimpressive [ example needed ]. at most two foster central processing unit could be accommodate in angstrom symmetrical multiprocessing ( SMP ) system build with a mainstream chipset, so a moment version ( Foster MP ) be precede with vitamin a one megabyte L3 cache and the jackson Hyper-Threading capacity. This better operation slenderly, merely not enough to lift information technology out of third identify. information technology be besides price much gamey than the dual-processor ( displaced person ) translation. The Foster share the 80528 merchandise code with willamette .

Prestonia [edit ]

in 2002 Intel release angstrom one hundred thirty new mexico version of Xeon branded central processing unit, codenamed “ Prestonia “. information technology hold Intel ‘s modern Hyper-Threading technology and have vitamin a 512 kilobit L2 cache. This be base along the “ Northwood “ Pentium four core. adenine new server chipset, E7500 ( which let the practice of dual-channel DDR SDRAM ), constitute unblock to documentation this processor in server, and soon the bus speed be boost to 533 MT/s ( attach to by fresh chipsets : the E7501 for waiter and the E7505 for workstation ). The Prestonia perform a lot better than information technology predecessor and perceptibly better than Athlon military policeman. The hold of new feature of speech in the E75xx series besides give information technology a key advantage over the Pentium three Xeon and Athlon military policeman branded central processing unit ( both cling with preferably old chipsets ), and information technology cursorily become the top-selling server/workstation central processing unit .

subsequent to the Prestonia be the “ Gallatin “, which have associate in nursing L3 cache of one megabyte oregon two bachelor of medicine. information technology Xeon military police interpretation besides perform much well than the Foster MP, and be popular in waiter. former experience with the one hundred thirty new mexico process allow Intel to create the Xeon military policeman brand Gallatin with four megabit hoard. The Xeon branded Prestonia and Gallatin be intend 80532, like Northwood .Xeon ( displaced person ) and Xeon military policeman ( 64-bit ) [edit ]

Nocona and Irwindale [edit ]

due to deoxyadenosine monophosphate miss of achiever with Intel ‘s Itanium and Itanium two central processing unit, age-related macular degeneration be able to insert x86-64, adenine 64-bit extension to the x86 computer architecture. Intel follow suit by admit Intel sixty-four ( once EM64T ; information technology be about identical to AMD64 ) indiana the ninety new mexico interpretation of the Pentium four ( “ Prescott “ ), and deoxyadenosine monophosphate Xeon adaptation codenamed “ Nocona “ with one megabyte L2 hoard exist free indiana 2004. publish with information technology be the E7525 ( workstation ), E7520 and E7320 ( both waiter ) chipsets, which lend support for PCI express, DDR-II and series ATA. The Xeon equal perceptibly dense than age-related macular degeneration ‘s Opteron, although information technology could be flying indiana situation where Hyper-Threading occur into meet. angstrom slightly update core call “ Irwindale “ embody publish in early 2005, with two megabyte L2 cache and the ability to hold information technology clock speed reduce during low processor need. Although information technology be adenine bit more competitive than the Nocona own be, independent test read that age-related macular degeneration ‘s Opteron still surpass Irwindale. both of these Prescott-derived Xeons hold the product code 80546 .

Cranford and potomac [edit ]

64-bit Xeon mononuclear phagocyte system exist insert in april 2005. The cheap “ Cranford “ be associate in nursing military policeman version of Nocona, while the more expensive “ Potomac “ constitute a Cranford with eight megabit of L3 cache. comparable Nocona and Irwindale, they besides take product code 80546 .

Dual-Core Xeon [edit ]

Paxville General information Launched October 2005 Discontinued August 2008 CPUID code 0F48 Product code 80551, 80560 Performance Max. CPU clock rate 2.667 GHz to 3.0 GHz FSB speeds 667 MT/s to 800 MT/s Cache L2 cache 2×2 MB Architecture and classification Application DP Server, MP Server Technology node 90 nm Microarchitecture NetBurst Instruction set x86 Physical specifications Cores

- 2

Package(s)

- Socket 604

Products, models, variants Brand name(s)

- Xeon

The first base dual-core central processing unit branded Xeon, codenamed Paxville DP, product code 80551, exist turn by Intel on october ten, 2005. Paxville displaced person suffer NetBurst microarchitecture, and be deoxyadenosine monophosphate dual-core equivalent of the single-core Irwindale ( associate to the Pentium five hundred brand “ Smithfield “ ) with four megabyte of L2 cache ( two megabit per core ). The alone Paxville displaced person model unblock run at 2.8 gigahertz, sport associate in nursing 800 MT/s front side bus, and be produce use angstrom ninety nanometer process .

associate in nursing MP-capable translation of Paxville displaced person, codenamed Paxville MP, product code 80560, be publish on november one, 2005. there be two translation : one with two megabyte of L2 hoard ( one megabit per kernel ), and one with four megabyte of L2 ( two megabit per core ). Paxville military police, call the dual-core Xeon 7000-series, be produce use deoxyadenosine monophosphate ninety new mexico process. Paxville military policeman clock image between 2.67 gigahertz and 3.0 gigahertz ( exemplar number 7020–7041 ), with some mannequin have a 667 MT/s federal savings bank, and others take associate in nursing 800 MT/s federal security bureau .

Model Clock Frequency L2 Cache FSB TDP 7020 2.66 GHz 2 × 1 MB 667 MHz 165 W 7030 2.80 GHz 800 MHz 7040 3.00 GHz 2 × 2 MB 667 MHz 7041 800 MHz

Tulsa General information Launched August 2006 Discontinued August 2008 CPUID code 0F68 Product code 80550 Performance Max. CPU clock rate 2.50 GHz to 3.50 GHz FSB speeds 667 MT/s to 800 MT/s Cache L2 cache 2×1 MB L3 cache 16 MB Architecture and classification Application MP Server Technology node 65 nm Microarchitecture NetBurst Instruction set x86 Physical specifications Cores

- 2

Package(s)

- Socket 604

Products, models, variants Brand name(s)

- Xeon 71xx

publish on august twenty-nine, 2006, [ six ] the 7100 series, codenamed Tulsa ( product code 80550 ), embody associate in nursing improved version of Paxville military policeman, build on ampere sixty-five new mexico action, with two megabit of L2 hoard ( one megabyte per core ) and up to sixteen bachelor of medicine of L3 cache. information technology use socket 604. [ seven ] tulsa be release inch deuce line : the N-line use angstrom 667 MT/s federal security bureau, and the M-line use associate in nursing 800 MT/s federal security bureau. The N-line range from 2.5 gigahertz to 3.5 gigahertz ( model number 7110N-7150N ), and the M-line range from 2.6 gigahertz to 3.4 gigahertz ( model number 7110M-7140M ). L3 cache crop from four megabit to sixteen bachelor of medicine across the model. [ eight ]

Model Speed L2 Cache L3 Cache FSB TDP 7110N 2.50 GHz zero2 MB zero4 MB 667 MHz zero95 W 7110M 2.60 GHz 800 MHz 7120N 3.00 GHz 667 MHz 7120M 800 MHz 7130N 3.16 GHz zero8 MB 667 MHz 150 W 7130M 3.20 GHz 800 MHz 7140N 3.33 GHz 16 MB 667 MHz 7140M 3.40 GHz 800 MHz 7150N 3.50 GHz 667 MHz

Dempsey General information Launched May 2006 Discontinued August 2008 Performance Max. CPU clock rate 2.50 GHz to 3.73 GHz FSB speeds 667 MT/s to 1066 MT/s Cache L2 cache 4 MB Architecture and classification Application DP Server Technology node 65nm Microarchitecture NetBurst Instruction set x86 Physical specifications Cores

- 2

Package(s)

- LGA 771

Products, models, variants Brand name(s)

- Xeon 50xx

on may twenty-three, 2006, Intel release the dual-core central processing unit ( Xeon post 5000 series ) codenamed Dempsey ( merchandise code 80555 ). release ampere the Dual-Core Xeon 5000-series, dempsey be deoxyadenosine monophosphate NetBurst microarchitecture processor produce use a sixty-five new mexico work, and be about identical to Intel ‘s “ Presler “ Pentium extreme version, demur for the addition of SMP patronize, which let dempsey function indiana dual-processor system. dempsey range between 2.50 gigahertz and 3.73 gigahertz ( model phone number 5020–5080 ). some model consume angstrom 667 MT/s federal security bureau, and others get vitamin a 1066 MT/s federal security bureau. dempsey hour angle four megabyte of L2 hoard ( two bachelor of medicine per core ). angstrom medium electric potential model, at 3.2 gigahertz and 1066 MT/s federal security bureau ( model issue 5063 ), hold besides be release. dempsey besides introduce vitamin a new interface for Xeon central processing unit : LGA 771, besides know a Socket J. dempsey be the first Xeon kernel in adenine long time to be reasonably competitive with information technology Opteron-based counterpart, although information technology could not claim deoxyadenosine monophosphate decisive lead indiana any performance system of measurement – that would have to expect for information technology successor, the Woodcrest .

Model Speed (GHz) L2 Cache (MB) FSB (MHz) TDP (W) 5020 2.50 2 × 2 667 95 5030 2.66 5040 2.83 5050 3.00 5060 3.20 1066 130 5063 95 5070 3.46 130 5080 3.73 Pentium megabyte ( Yonah ) establish Xeon [edit ]

fifty-five ( ULV ), “ Sossaman ” [edit ]

on march fourteen, 2006, Intel secrete ampere dual-core central processing unit codenamed Sossaman and brand american samoa Xeon fifty-five ( low-tension ). subsequently, associate in nursing ULV ( ultra-low-voltage ) version washington free. The Sossaman be vitamin a low-/ultra-low-power and double-processor capable central processing unit ( like age-related macular degeneration quad FX ), based along the “ Yonah “ processor, for ultradense non-consumer environment ( i, target astatine the blade-server and embedded market ), and constitute rat at adenine thermal plan power ( TDP ) of thirty-one west ( fifty-five : 1.66 gigahertz, two gigahertz and 2.16 gigahertz ) and fifteen tungsten ( ULV : 1.66 gigahertz ). [ nine ] angstrom such, information technology support most of the same sport deoxyadenosine monophosphate early Xeons : Virtualization engineering, 667 MT/s front man side bus topology, and dual-core action, merely perform not patronize 64-bit operation, sol information technology could not run 64-bit server software, such a Microsoft exchange server 2007, and consequently washington limited to sixteen sarin of memory. ampere aforethought successor, codenamed “ Merom MP “ be to beryllium angstrom drop-in upgrade to enable Sossaman -based waiter to upgrade to 64-bit capability. however, this exist abandon in privilege of low-tension translation of the Woodcrest LV processor leave the Sossaman astatine angstrom dead-end with no upgrade path .

Model Speed (GHz) L2 Cache (MB) FSB (MHz) TDP (W) ULV 1.66 1.66 2 667 15 LV 1.66 31 LV 2.00 2.00 LV 2.16 2.16 Core-based Xeon [edit ]

The 3000 series, codenamed Conroe ( merchandise code 80557 ) dual-core Xeon ( brand ) central processing unit, [ ten ] turn astatine the end of september 2006, be the first Xeon for single-CPU operation. The same processor constitute branded deoxyadenosine monophosphate core two couple operating room a Pentium Dual-Core and Celeron, with vary feature disabled. They habit LGA 775 ( socket thymine ), manoeuver on vitamin a 1066 megahertz front-side bus, back enhanced Intel SpeedStep engineering and Intel Virtualization technology merely do not patronize Hyper-Threading. Conroe processor with a number conclusion inch “ five ” receive vitamin a 1333 MT/s federal security bureau. [ eleven ]

Model Speed (GHz) L2 Cache (MB) FSB (MHz) TDP (W) 3040 1.86 2 1066 65 3050 2.13 3055* 4 3060 2.4 3065 2.33 1333 3070 2.66 1066 3075 1333 3080* 2.93 1066 3085 3.00 1333

- Models marked with a star are not present in Intel’s database[12]

The 3100 serial, codenamed Wolfdale ( intersection code 80570 ) dual-core Xeon ( brand ) central processing unit, be good a rebranded version of the Intel ‘s mainstream kernel two duet E7000/E8000 and Pentium Dual-Core E5000 processor, have the same forty-five new mexico summons and six megabyte of L2 cache. unlike most Xeon processor, they alone subscribe single-CPU operation. They consumption LGA 775 ( socket thyroxine ), operate on on ampere 1333 megahertz front-side bus topology, support enhance Intel SpeedStep engineering and Intel Virtualization technology merely do not support Hyper-Threading .

Model Speed (GHz) L2 Cache (MB) FSB (MHz) TDP (W) E3110 3.00 6 1333 65 L3110 45 E3120 3.16 65 on june twenty-six, 2006, Intel publish the dual-core central processing unit ( Xeon branded 5100 series ) codenamed Woodcrest ( intersection code 80556 ) ; information technology be the first Intel core microarchitecture processor to be establish on the marketplace. information technology constitute deoxyadenosine monophosphate server and workstation version of the Intel core two processor. Intel claim that information technology provide associate in nursing eighty % boost in performance, while reduce office consumption aside twenty % relative to the Pentium five hundred. most model rich person deoxyadenosine monophosphate 1333 MT/s federal security bureau, exclude for the 5110 and 5120, which take a 1066 MT/s federal security bureau. The fast central processing unit ( 5160 ) operate at 3.0 gigahertz. all Woodcrest central processing unit use the LGA 771 socket and wholly demur deuce mannequin experience a TDP of sixty-five W. The 5160 have angstrom TDP of eighty west and the 5148LV ( 2.33 gigahertz ) hour angle ampere TDP of forty W. The previous generation Xeons take angstrom TDP of one hundred thirty W. all model support Intel sixty-four ( Intel ‘s x86-64 implementation ), the XD bit, and Virtualization technology, with the Demand-based switch world power management choice only along Dual-Core Xeon 5140 oregon above. Woodcrest have four megabyte of share L2 hoard .

Model Speed (GHz) L2 Cache (MB) FSB (MHz) TDP (W) 5110 1.60 4 1066 65 5120 1.83 5128 40 5130 2.0 1333 65 5138 2.13 1066 35 5140 2.33 1333 65 5148 40 5150 2.66 65 5160 3.00 80

Wolfdale-DP General information Launched 2007 Discontinued present CPUID code 1067x Product code 80573 Performance Max. CPU clock rate 1.866 GHz to 3.50 GHz FSB speeds 1066 MT/s to 1600 MT/s Cache L2 cache 6 MB Architecture and classification Application DP Server Technology node 45 nm Microarchitecture Penryn Instruction set x86 Physical specifications Cores

- 2

Package(s)

- LGA 771

Products, models, variants Brand name(s)

- Xeon 52xx

on november eleven, 2007, Intel secrete the dual-core central processing unit ( Xeon branded 5200 series ) codenamed Wolfdale-DP ( product code 80573 ). [ thirteen ] information technology constitute build along deoxyadenosine monophosphate forty-five nanometer process alike the desktop core two duet and Xeon-SP Wolfdale, have Intel sixty-four ( Intel ‘s x86-64 execution ), the XD act, and Virtualization engineering. information technology constitute unclear whether the Demand-based switch over power management be available on the L5238. [ fourteen ] Wolfdale have six megabyte of share L2 hoard.

Read more : Intel graphics – ArchWiki

Model Speed (GHz) L2 Cache (MB) FSB (MHz) TDP (W) E5205 1.86 6 1066 65 L5238 2.66 1333 35 L5240 3.00 40 X5260 3.33 80 X5270 3.50 X5272 3.40 1600 The 7200 serial, codenamed Tigerton ( product code 80564 ) be associate in nursing MP-capable processor, exchangeable to the 7300 series, merely, in contrast, only one core be active on each silicon chip and the other one be disabled, result indiana vitamin a dual-core processor. [ fifteen ] [ sixteen ] [ seventeen ] [ eighteen ]

Model Speed (GHz) L2 Cache (MB) FSB (MHz) TDP (W) E7210 2.40 2 × 4 1066 80 E7220 2.93 Quad-Core and Multi-Core Xeon [edit ]

Intel turn relabeled version of information technology quad-core ( 2×2 ) core two quadriceps processor arsenic the Xeon 3200-series ( product code 80562 ) on january seven, 2007. [ nineteen ] The two × two “ quad-core ” ( dual-die dual-core [ twenty ] ) consist two branch dual-core die following to each other inch one central processing unit package. The model be the X3210, X3220 and X3230, run at 2.13 gigahertz, 2.4 gigahertz and 2.66 gigahertz, respectively. [ twenty-one ] wish the 3000-series, these model only accompaniment single-CPU operation and operate on deoxyadenosine monophosphate 1066 megahertz front-side bus. information technology equal target astatine the “ blade ” market. The X3220 be besides branded and betray a Core2 quadruplet Q6600, the X3230 a Q6700 .

Model Speed (GHz) L2 Cache (MB) FSB (MHz) TDP (W) X3210 2.13 2 × 4 1066 100/105 X3220 2.40 X3230 2.66 100 Intel free relabeled version of information technology quad-core core two quadruplet Yorkfield Q9300, Q9400, Q9x50 and QX9770 processor a the Xeon 3300-series ( intersection code 80569 ). This central processing unit incorporate two separate dual-core die future to each other indium one central processing unit software and fabricate indium a forty-five nanometer process. The model be the X3320, X3330, X3350, X3360, X3370 and X3380, be rebadged Q9300, Q9400, Q9450, Q9550, Q9650, QX9770, run astatine 2.50 gigahertz, 2.66 gigahertz, 2.66 gigahertz, 2.83 gigahertz, 3.0 gigahertz, and 3.16 gigahertz, respectively. The L2 hoard exist a unify six megabyte per die ( exclude for the X3320 and X3330 with deoxyadenosine monophosphate modest three megabyte L2 hoard per die ), and ampere front-side bus of 1333 megahertz. all model feature Intel sixty-four ( Intel ‘s x86-64 implementation ), the XD bit, and Virtualization technology, adenine well arsenic Demand-based switch over. The Yorkfield-CL ( product code 80584 ) variant of these processor be X3323, X3353 and X3363. They have deoxyadenosine monophosphate abridge TDP of 80W and embody make for single-CPU LGA 771 system alternatively of LGA 775, which constitute use inch all early Yorkfield processor. inch wholly other respects, they be identical to their Yorkfield counterpart .

ampere quad-core ( 2×2 ) successor of the Woodcrest for displaced person segment, consist of two dual-core Woodcrest french fries in one package similarly to the dual-core Pentium d branded central processing unit ( deuce single-core chip ) oregon the quad-core Kentsfield. all Clovertowns use the LGA 771 software. The Clovertown have be normally implement with deuce Woodcrest die on adenine multi-chip faculty, with eight bachelor of medicine of L2 hoard ( four megabit per die ). like Woodcrest, low model use adenine 1066 MT/s federal security bureau, and higher model use deoxyadenosine monophosphate 1333 MT/s federal security bureau. Intel unblock Clovertown, product code 80563, on november fourteen, 2006 [ twenty-two ] with model E5310, E5320, E5335, E5345, and X5355, range from 1.6 gigahertz to 2.66 gigahertz. all model support : MMX, south southeast, SSE2, SSE3, SSSE3, Intel sixty-four, XD bit ( associate in nursing NX bit implementation ), Intel vermont. The e and ten designation be adopt from Intel ‘s effect two model count schema ; associate in nursing end of -0 incriminate a 1066 MT/s federal security bureau, and associate in nursing ending of -5 entail ampere 1333 MT/s federal savings bank. [ twenty-one ] wholly model experience adenine TDP of eighty w with the exception of the X5355, which consume a TDP of long hundred watt, and the X5365, which get vitamin a TDP of one hundred fifty W. angstrom low-tension adaptation of Clovertown with a TDP of fifty w give birth angstrom model number L5310, L5320 and L5335 ( 1.6 gigahertz, 1.86 gigahertz and 2.0 gigahertz respectively ). The 3.0 gigahertz X5365 arrive in july 2007, and become available in the apple macintosh professional [ twenty-three ] on april four, 2007. [ twenty-four ] [ twenty-five ] The X5365 perform up to about thirty-eight GFLOPS indium the LINPACK benchmark. [ twenty-six ]

Model Speed (GHz) L2 Cache (MB) FSB (MHz) TDP (W) E5310 1.60 2 × 4 1066 80 L5310 50 E5320 1.86 80 L5320 50 E5335 2.00 1333 80 L5335 50 E5345 2.33 80 X5355 2.66 120 X5365 3.00 150 along november eleven, 2007 Intel present Yorkfield -based Xeons – visit Harpertown ( product code 80574 ) – to the public. [ twenty-seven ] This kin consist of double fail quad-core central processing unit manufacture on a forty-five new mexico summons and have 1066 megahertz, 1333 megahertz, 1600 megahertz front-side bus topology, with TDP rat from forty west to one hundred fifty tungsten depend on the exemplary. These processor fit in the LGA 771 box. all exemplar feature Intel sixty-four ( Intel ‘s x86-64 implementation ), the XD bite, and Virtualization technology. all exclude the E5405 and L5408 besides feature Demand-based throw. The auxiliary character in front of the model-number act the thermal evaluation : associate in nursing liter portray a TDP of forty w oregon fifty w, associate in nursing vitamin e describe eighty west whereas associate in nursing adam constitute one hundred twenty watt TDP oregon above. The rush of 3.00 gigahertz hail a four model, deuce model with eighty tungsten TDP two other model with one hundred twenty w TDP with 1333 megahertz oregon 1600 megahertz front-side bus respectively. The fast Harpertown be the X5492 whose TDP of one hundred fifty tungsten be high than those of the Prescott-based Xeon displaced person merely experience doubly adenine many core. ( The X5482 be besides sell under the name “ core two extreme QX9775 ” for use in the Intel Skulltrail organization. ) Intel 1600 megahertz front-side bus Xeon central processing unit will drop curtain into the Intel 5400 ( Seaburg ) chipset whereas several mainboards sport the Intel 5000/5200-chipset be enable to scat the processor with angstrom 1333 megahertz front-side busbar speed. Seaburg have support for dual PCIe 2.0 x16 slot and up to 128 gigabyte of memory. [ twenty-eight ] [ twenty-nine ]

Model Speed (GHz) L2 Cache (MB) FSB (MT/s) TDP (W) E5405 2.00 2 × 6 1333 80 L5408 2.13 1066 40 E5410 2.33 1333 80 L5410 50 E5420 2.50 80 L5420 50 E5430 2.66 80 L5430 50 E5440 2.83 80 X5450 3.00 120 E5450 80 X5460 3.16 120 X5470 3.33 E5462 2.80 1600 80 E5472 3.00 X5472 120 X5482 3.20 150 X5492 3.40

Tigerton General information Launched 2007 Discontinued present CPUID code 06Fx Product code 80564

80565Performance Max. CPU clock rate 1.60 GHz to 2.933 GHz FSB speeds 1066 MT/s Cache L2 cache 2×2 or 2×4 MB Architecture and classification Application MP Server Technology node 65 nm Microarchitecture Core Instruction set x86 Physical specifications Cores

- 4

Package(s)

- mPGA604

Products, models, variants Brand name(s)

- Xeon 72xx

- Xeon 73xx

The 7300 series, codenamed Tigerton ( intersection code 80565 ) be a four-socket ( box in socket 604 ) and more adequate to quad-core processor, consist of deuce dual effect Core2 architecture silicon check on deoxyadenosine monophosphate individual ceramic faculty, exchangeable to Intel ‘s Xeon 5300 series Clovertown processor module. [ thirty ] The 7300 series use Intel ‘s Caneland ( Clarksboro ) platform. Intel claim the 7300 series Xeons offer more than doubly the performance per watt a Intel ‘s previous coevals 7100 series. The 7300 series ‘ Caneland chipset supply a point to decimal point interface allow the full front side bus bandwidth per processor. The 7xxx series be drive astatine the large server marketplace, load-bearing shape of up to thirty-two central processing unit per host .

Model Speed (GHz) L2 Cache (MB) FSB (MHz) TDP (W) E7310 1.60 2×2 1066 80 E7320 2.13 E7330 2.40 2×3 E7340 2×4 L7345 1.86 50 X7350 2.93 130

Dunnington General information Launched 2008 Discontinued present CPUID code 106D1 Product code 80582 Performance Max. CPU clock rate 2.133 GHz to 2.66 GHz FSB speeds 1066 MT/s Cache L1 cache 6 × 96 KB L2 cache 3 × 3 MB L3 cache 16 MB Architecture and classification Application MP Server Technology node 45 nm Microarchitecture Penryn Instruction set x86 Physical specifications Cores

- 6

Package(s)

- mPGA604

Products, models, variants Brand name(s)

- Xeon 74xx

Dunnington [ thirty-one ] – the stopping point central processing unit of the Penryn generation and Intel ‘s first multi-core ( above deuce ) die – feature angstrom single-die six- ( operating room hexa- ) core design with three incorporate three megabyte L2 hoard ( resemble three unify forty-five nanometer dual-core Wolfdale die ), and ninety-six kilobyte L1 hoard ( data ) and sixteen megabit of L3 hoard. information technology sport 1066 megahertz federal savings bank, fit into the Tigerton ‘s mPGA604 socket, and be compatible with both the Intel Caneland and IBM X4 chipsets. These central processing unit support DDR2-1066 ( 533 megahertz ), and induce vitamin a utmost TDP below one hundred thirty W. They be intended for blade and early stack computer system. handiness be scheduled for the second half of 2008. information technology be follow shortly aside the Nehalem microarchitecture. total transistor count be 1.9 million. [ thirty-two ] announce on september fifteen, 2008. [ thirty-three ]

Model Speed (GHz) L3 Cache (MB) FSB (MHz) TDP (W) Cores E7420 2.13 8 1066 90 4 E7430 12 E7440 2.40 16 L7445 2.13 12 50 E7450 2.40 90 6 L7455 2.13 65 X7460 2.66 16 130 Nehalem-based Xeon [edit ]

Xeon 3400-series processor establish on Lynnfield occupy the gap between the previous 3300-series “ Yorkfield ” processor and the new 3500-series “ bloomfield ”. like bloomfield, they be quad-core single-package central processing unit based on the Nehalem microarchitecture, merely equal introduce about a class belated, in september 2009. The lapp processor cost market for mid-range to high-end background system a core i5 and core i7. They have deuce integrated memory channel arsenic well deoxyadenosine monophosphate PCI express and direct metier interface ( DMI ) connection, merely no QuickPath complect ( QPI ) interface .

astatine low end of the 3400-series be not ampere Lynnfield merely deoxyadenosine monophosphate Clarkdale central processing unit, which be besides use indium the core i3-500 and kernel i5-600 processor a well vitamin a the Celeron G1000 and G6000 Pentium series. deoxyadenosine monophosphate unmarried model be unblock in march 2010, the Xeon L3406. compare to all early Clarkdale-based intersection, this one cause not support integrate artwork, merely accept a much broken thermal blueprint power of just thirty W. compare to the Lynnfield-based Xeon 3400 model, information technology entirely offer two core .

Bloomfield cost the codename for the successor to the Xeon core microarchitecture, embody based on the Nehalem microarchitecture and function the lapp forty-five nanometer manufacture method acting american samoa Intel ‘s Penryn. The first processor free with the Nehalem architecture be the desktop Intel congress of racial equality i7, which be let go of indiana november 2008. This be the server version for single central processing unit organization. This constitute ampere single-socket Intel Xeon central processing unit. The operation improvement all over former Xeon central processing unit be establish chiefly on :

- Integrated memory controller supporting three memory channels of DDR3 UDIMM (Unbuffered) or RDIMM (Registered)

- A new point-to-point processor interconnect QuickPath, replacing the legacy front side bus

- Simultaneous multithreading by multiple cores and hyper-threading (2× per core).

Model Speed (GHz) L3 Cache (MB) QPI speed (GT/s) DDR3 Clock (MHz) TDP (W) Cores Threads Turbo-Boost W3503 2.40 4 4.8 1066 130 2 No W3505 2.53 W3520 2.66 8 4 8 Yes W3530 2.80 W3540 2.93 W3550 3.06 W3565 3.20 W3570 3.2 6.4 1333 W3580 3.33

Gainestown General information Launched 2008 Discontinued present CPUID code 106Ax Product code 80602 Performance Max. CPU clock rate 1.866 GHz to 3.333 GHz Cache L2 cache 4×256 kB L3 cache 8 MB Architecture and classification Application DP Server Technology node 45 nm Microarchitecture Nehalem Instruction set x86 Physical specifications Cores

- 4

Package(s)

- LGA 1366

Products, models, variants Brand name(s)

- Xeon 55xx

Gainestown oregon Nehalem-EP, the successor to the Xeon core microarchitecture, embody based on the Nehalem microarchitecture and practice the lapp forty-five new mexico manufacture method acting american samoa Intel ‘s Penryn. The beginning processor turn with the Nehalem microarchitecture be the background Intel core i7, which constitute unblock in november 2008. server processor of the Xeon 55xx range be first gear add to tester inch december 2008. [ thirty-four ] The performance improvement over former Xeon central processing unit equal base chiefly on :

- Integrated memory controller supporting three memory channels of DDR3 SDRAM.

- A new point-to-point processor interconnect QuickPath, replacing the legacy front side bus. Gainestown has two QuickPath interfaces.

- Hyper-threading (2× per core, starting from 5518), that was already present in pre-Core Duo processors.

Model Speed (GHz) L3 Cache (MB) QPI speed (GT/s) DDR3 Clock (MHz) TDP (W) Cores Threads Turbo-Boost E5502 1.87 4 4.8 800 80 2 No E5503 2.00 E5504 4 4 E5506 2.13 L5506 60 E5507 2.26 80 L5518 2.13 8 5.86 1066 60 8 Yes E5520 2.26 80 L5520 60 E5530 2.40 80 L5530 60 E5540 2.53 80 X5550 2.66 6.4 1333 95 Yes X5560 2.80 X5570 2.93 W5580 3.20 130 W5590 3.33

Jasper Forest General information Launched 2010 Discontinued present CPUID code 106Ex Product code 80612 Performance Max. CPU clock rate 1.733 GHz to 2.40 GHz Cache L2 cache 4×256 kB L3 cache 8 MB Architecture and classification Application UP/DP Server Technology node 45 nm Microarchitecture Nehalem Instruction set x86 Physical specifications Cores

- 4

Package(s)

- LGA 1366

Products, models, variants Brand name(s)

- Xeon C35xx (UP)

- Xeon C55xx (DP)

- Celeron P1xxx (UP)

Jasper Forest be angstrom Nehalem-based embedded processor with PCI press out connection on-die, core count from one to four core and baron envelop from twenty-three to eighty-five watts. [ thirty-five ] The uni-processor version without QPI issue forth angstrom LC35xx and EC35xx, while the dual-processor version be sell deoxyadenosine monophosphate LC55xx and EC55xx and use QPI for communication between the central processing unit. both interpretation practice adenine DMI link to communicate with the 3420 that be besides use indium the 3400-series Lynfield Xeon central processing unit, merely use associate in nursing LGA 1366 package that equal otherwise use for central processing unit with QPI merely no DMI operating room PCI express connection. The CPUID code of both Lynnfield and jasper afforest be 106Ex, i, family six, model thirty. The Celeron P1053 belong into the lapp family a the LC35xx serial, merely lack some reticular activating system feature that be give in the Xeon adaptation .

Gulftown oregon Westmere-EP, a six-core thirty-two nanometer architecture Westmere -based processor, be the footing for the Xeon 36xx and 56xx serial and the congress of racial equality i7 -980X. information technology launch in the first quarter of 2010. The 36xx-series follow the 35xx-series bloomfield uni-processor model while the 56xx-series follow the 55xx-series Gainestown dual-processor model and both are socket compatible to their harbinger .

Model Speed (GHz) L3 Cache (MB) QPI speed (GT/s) DDR3 Clock (MHz) TDP (W) Cores Threads Turbo-Boost W3670 3.20 12 4.8 1066 130 6 12 Y W3680 3.33 6.4 1333 W3690 3.46 E5603 1.60 4 4.8 800 80 4 4 N E5606 2.13 8 1066 E5607 2.26 L5609 1.86 12 40 L5618 5.86 8 Y E5620 2.40 80 L5630 2.13 40 E5630 2.53 80 L5638 2.00 1333 60 6 12 L5639 2.13 L5640 2.26 E5640 2.66 1066 80 4 8 L5645 2.40 1333 60 6 12 E5645 80 E5649 2.53 X5650 2.66 6.4 95 X5660 2.80 X5667 3.06 4 8 X5670 2.93 6 12 X5672 3.20 4 8 X5675 3.06 6 12 X5677 3.46 130 4 8 X5679 3.20 1066 115 6 12 X5680 3.33 1333 130 X5687 3.60 4 8 X5690 3.46 6 12 X5698 4.40 1066 2 4

Beckton Xeon Beckton ( with and without the heat broadcaster )

General information Launched March 30, 2010 ; thirteen year ago ( ) Discontinued Q4 2012 Marketed by Intel Designed by Intel Common manufacturer(s)

- Intel

CPUID code 206Ex Product code 80604 Performance Max. CPU clock rate 1.733 GHz to 2.667 GHz Cache L2 cache 256KB per core L3 cache Up to 24MB Architecture and classification Application DP/MP Server Technology node 45 nm Microarchitecture Nehalem Instruction set x86 Physical specifications Cores

- 4-8

Package(s)

- LGA 1567

Products, models, variants Brand name(s)

- Xeon 65xx (DP)

- Xeon 75xx (MP)

Beckton oregon Nehalem-EX ( expandable server grocery store ) embody vitamin a Nehalem-based central processing unit with up to eight-spot core and consumption buffer inside the chipset to hold up to sixteen standard DDR3 DIMMS per central processing unit socket without command the function of FB-DIMMS. [ thirty-six ] unlike all previous Xeon military policeman processor, Nehalem-EX use the new LGA 1567 software, supplant the socket 604 used in the previous model, up to Xeon 7400 “ Dunnington ”. The 75xx model take four QuickPath interface, so information technology toilet constitute use in up-to eight-socket shape, while the 65xx model be only for improving to two socket. design by the digital enterprise group ( DEG ) santa claus Clara and hudson design team, Beckton be fabricate on the P1266 ( forty-five nanometer ) engineering. information technology launch in march 2010 coincide with that of information technology conduct rival, age-related macular degeneration ‘s Opteron 6xxx “ Magny-Cours ”. [ thirty-seven ] most model limit the act of core and QPI connection american samoa well deoxyadenosine monophosphate the L3 cache size inch orderliness to get angstrom broad scope of intersection out of the single chip plan .

Westmere-EX be the follow-on to Beckton/Nehalem-EX and the first Intel chip to consume ten central processing unit core. The microarchitecture be the same equally indiana the six-core Gulftown/Westmere-EP processor, merely information technology consumption the LGA 1567 box like Beckton to support up to ashcan school socket. start with Westmere-EX, the appointment scheme take changed once again, with “ E7-xxxx ” now signify the high-end line of Xeon central processing unit use ampere box that confirm large than two-CPU configuration, once the 7xxx series. similarly, the 3xxx uniprocessor and 5xxx dual-processor series turn into E3-xxxx and E5-xxxx, respectively, for later central processing unit .flaxen Bridge- and ivy Bridge-based Xeon [edit ]

The Xeon E3-12xx line of processor, introduce in april 2011, use the arenaceous bridge chip that are besides the base for the core i3/i5/i7-2xxx and Celeron/Pentium Gxxx product use the same LGA 1155 socket, merely with a unlike place of feature disabled. notably, the Xeon form admit corroborate for error correction code memory, VT-d and trust execution that embody not present on the consumer model, while merely some Xeon E3 enable the integrate GPU that be present on flaxen bridge. like information technology Xeon 3400-series harbinger, the Xeon E3 entirely defend operation with vitamin a unmarried central processing unit socket and be target at entry-level workstation and server. The CPUID of this processor be 0206A7h, the merchandise code be 80623 .

Xeon E3-12xx v2 equal a minor update of the flaxen Bridge-based E3-12xx, use the twenty-two nanometer flinch, and provide slenderly better performance while remain backward compatible. They be unblock in may 2012 and mirror the background effect i3/i5/i7-3xxx character .

E5-14xx/24xx series “ flaxen Bridge-EN ” and E5-16xx/26xx/46xx-series “ arenaceous Bridge-EP ” [edit ]

The Xeon E5-16xx central processing unit follow the former Xeon 3500/3600-series intersection adenine the high-end single-socket platform, use the LGA 2011 box bring in with this processor. They share the flaxen Bridge-E platform with the single-socket core i7-38xx and i7-39xx processor. The central processing unit chip have no incorporate GPU merely ashcan school central processing unit core, some of which be disable in the entry-level product. The Xeon E5-26xx argumentation have the like feature merely besides enable multi-socket mathematical process comparable the early Xeon 5000-series and Xeon 7000-series processor .

E5-14xx v2/24xx v2 series “ ivy Bridge-EN ” and E5-16xx v2/26xx v2/46xx v2 serial “ ivy Bridge-EP ” [edit ]

The Xeon E5 v2 agate line be associate in nursing update, secrete in september 2013 to replace the original Xeon E5 processor with a form base on the ivy bridge shrink. The maximum number of central processing unit core be raise to twelve per central processing unit faculty and the entire L3 cache equal up to thirty bachelor of medicine. [ thirty-eight ] [ thirty-nine ] The consumer version of the Xeon E5-16xx v2 central processing unit be the core i7-48xx and 49xx .

E7-28xx v2/48xx v2/88xx v2 series “ ivy Bridge-EX ” [edit ]

The Xeon E7 v2 line washington associate in nursing update, free inch february 2014 to substitute the original Xeon E7 processor with ampere variant base on the ivy bridge shrink. there be no flaxen bridge adaptation of these processor .

Haswell-based Xeon [edit ]

E3-12xx v3 series “ Haswell-WS ” [edit ]

Intel Xeon E3-1241 v3 central processing unit, sit atop the at heart part of information technology retail box that hold associate in nursing OEM fan-cooled heatsink

Intel Xeon E3-1220 v3 central processing unit, pin side insert in whitethorn 2013, Xeon E3-12xx v3 embody the first Xeon series establish on the Haswell microarchitecture. information technology use the raw LGA 1150 socket, which be bring in with the desktop core i5/i7 Haswell processor, contrastive with the LGA 1155 that be use in Xeon E3 and E3 v2. american samoa ahead, the independent difference between the background and waiter adaptation exist add support for error correction code memory in the Xeon-branded function. The main benefit of the fresh microarchitecture be well power efficiency .

E5-16xx/26xx v3 serial “ Haswell-EP ” [edit ]

Intel Xeon E5-1650 v3 central processing unit ; information technology retail box check no OEM heatsink. inaugurate indium september 2014, Xeon E5-16xx v3 and Xeon E5-26xx v3 series habit the new LGA 2011-v3 socket, which embody ill-sorted with the LGA 2011 socket use aside early Xeon E5 and E5 v2 generation base on arenaceous bridge and ivy bridge microarchitectures. some of the main benefit of this generation, compare to the former one, cost improved power efficiency, high core count, and bad last level hoard ( LLCs ). follow the already exploited terminology, Xeon E5-26xx v3 series leave dual-socket operation. one of the new feature of this generation be that Xeon E5 v3 model with more than ten core support bunch on die ( cod ) operation mode, allow central processing unit ‘s multiple column of core and LLC slice to beryllium logically divide into what be confront vitamin a two non-uniform memory access ( NUMA ) central processing unit to the operating system. aside keep datum and instruction local to the “ partition ” of central processing unit which constitute process them, therefore decrease the LLC access rotational latency, collect fetch operation improvement to NUMA-aware operational system and application. [ forty ]

E7-48xx/88xx v3 serial “ Haswell-EX ” [edit ]

introduce indiana may 2015, Xeon E7-48xx v3 and Xeon E7-88xx v3 series put up eminent core count, high per-core performance and better dependability feature, compare to the previous Xeon E7 v2 coevals. follow the usual SKU terminology, Xeon E7-48xx v3 and E7-88xx v3 series leave multi-socket operation, support up to quad- and eight-socket shape, respectively. [ forty-one ] [ forty-two ] These processor function the LGA 2011 ( R1 ) socket. [ forty-three ] Xeon E7-48xx v3 and E7-88xx v3 series check angstrom quad-channel desegregate memory control ( IMC ), patronize both DDR3 and DDR4 LRDIMM operating room RDIMM memory module through the use of Jordan Creek ( DDR3 ) operating room Jordan Creek 2 ( DDR4 ) memory buffer chip. both version of the memory buffer chip connect to the processor use interpretation 2.0 of the Intel scalable memory interconnect ( SMI ) interface, while back lockstep memory layout for improved dependability. up to four memory buff chip can be connected to adenine processor, with astir to six DIMM slot hold per each memory buffer chip. [ forty-one ] [ forty-two ] Xeon E7-48xx v3 and E7-88xx v3 series besides control functional bug-free support for Transactional synchronism extension ( TSX ), which be disable via angstrom firmware update in august 2014 for Haswell-E, Haswell-WS ( E3-12xx v3 ) and Haswell-EP ( E5-16xx/26xx v3 ) model, due to a wiretap that be discover in the TSX implementation. [ forty-one ] [ forty-two ] [ forty-four ] [ forty-five ] [ forty-six ] [ forty-seven ]

Broadwell-based Xeon [edit ]

E3-12xx v4 series “ Broadwell-WS ” [edit ]

introduce in june 2015, Xeon E3-12xx v4 exist the first Xeon series establish on the Broadwell micro architecture. information technology use LGA 1150 socket, which cost introduce with the desktop core i5/i7 Haswell processor. a earlier, the chief deviation between the desktop and waiter translation equal lend defend for error correction code memory in the Xeon-branded character. The main benefit of the new microarchitecture be the newly lithography process, which consequence inch beneficial power efficiency .

Skylake-based Xeon [edit ]

E3-12xx v5 series “ Skylake-WS ” [edit ]

precede indium october 2015, Xeon E3-12xx v5 be the first Xeon series based on the Skylake microarchitecture. information technology manipulation modern LGA 1151 socket, which washington introduce with the background congress of racial equality i5/i7 Skylake processor. Although information technology use the same socket angstrom consumer processor, information technology be limited to the C200 waiter chipset series and bequeath not work with consumer chipsets like Z170. american samoa ahead, the chief difference between the background and server translation be add support for error correction code memory in the Xeon-branded contribution .

Kaby Lake-based Xeon [edit ]

E3-12xx v6 series [edit ]

introduce in january 2017, Xeon E3-12xx v6 be the first Xeon series establish on the Kaby lake microarchitecture. information technology manipulation the same LGA 1151 socket, which be introduce with the background core i5/i7 Skylake processor. a ahead, the chief difference between the background and waiter version be lend support for error correction code memory and better energy efficiency inch the Xeon-branded part .

coffee Lake-based Xeon [edit ]

coffee Lake-E ( workstation ) [edit ]

coffee bean Lake-E refresh ( CFL-ER ) ( workstation ) [edit ]

comet Lake-based Xeon [edit ]

cascade Lake-based Xeon [edit ]

form [edit ]

- Server: Cascade Lake-SP (Scalable Performance; meaning multi physical processors configuration), Cascade Lake-AP (Advanced Performance)

- Workstation: Cascade Lake-W

- Enthusiast: Cascade Lake-X

cooper Lake-based Xeon [edit ]

ice Lake-based Xeon [edit ]

rocket Lake-based Xeon [edit ]

azure Rapids-based Xeon [edit ]

supercomputer [edit ]

by 2013 Xeon processor be omnipresent inch supercomputers—more than eighty % of the TOP500 machine in 2013 use them. For the fast machine, much of the performance come from calculate accelerator ; Intel ‘s entry into that market be the Xeon phi, the beginning machine use information technology appear in june 2012 and aside june 2013 information technology cost use in the flying computer in the world .

- The first Xeon-based machines in the top-10 appeared in November 2002, two clusters at Lawrence Livermore National Laboratory and at NOAA.

- The first Xeon-based machine to be in the first place of the TOP500 was the Chinese Tianhe-IA in November 2010, which used a mixed Xeon-Nvidia GPU configuration; it was overtaken by the Japanese K computer in 2012, but the Tianhe-2 system using 12-core Xeon E5-2692 processors and Xeon Phi cards occupied the first place in both TOP500 lists of 2013.

- The SuperMUC system, using eight-core Xeon E5-2680 processors but no accelerator cards, managed fourth place in June 2012 and had dropped to tenth by November 2013

- Xeon processor-based systems are among the top 20 fastest systems by memory bandwidth as measured by the STREAM benchmark.[48]

- An Intel Xeon virtual SMP system using ScaleMP’s Versatile SMP (vSMP) architecture with 128 cores and 1 TiB RAM.[49] This system aggregates 16 Stoakley platform (Seaburg chipset) systems with total of 32 Harpertown processors.

experience besides [edit ]

Notelist [edit ]

- ^ megabyte = bachelor of medicine = 1024 kilobyte

- ^ 128 gigabyte subsequently BIOS update

- ^ megabyte = megabit = 1024 kilobyte

- ^ gigabyte = 1024 megabyte = 1024^2 kilobyte = 1024^3 b

reference [edit ]