Central processing unit – Wikipedia

“ central processing unit ” redirect here. For other use, attend central processing unit ( disambiguation ) deoxyadenosine monophosphate central processing unit ( CPU ), besides visit ampere central processor operating room main processor, exist the most crucial processor in adenine give computer. information technology electronic circuitry execute instruction manual of deoxyadenosine monophosphate computer program, such deoxyadenosine monophosphate arithmetical, logic, control, and input/output ( I/O ) operation. This function contrast with that of external component, such deoxyadenosine monophosphate independent memory and I/O circuitry, [ one ] and specify coprocessors such a graphics action whole ( GPUs ) .

The form, plan, and execution of central processing unit have change over time, merely their fundamental operation remains about unaltered. principal component of deoxyadenosine monophosphate central processing unit include the arithmetic–logic unit ( ALU ) that perform arithmetic and logic operation, processor register that supply operand to the ALU and storehouse the resultant role of ALU process, and deoxyadenosine monophosphate control unit that mastermind the fetching ( from memory ), decode and execution ( of teaching ) by directing the coordinated operation of the ALU, file and other part.

Reading: Central processing unit – Wikipedia

most modern central processing unit be implement along desegregate circuit ( ninety-nine ) microprocessor, with one operating room more central processing unit on vitamin a single ninety-nine chip. microprocessor chip with multiple central processing unit be multi-core processor. The individual forcible central processing unit, processor cores, displace besides constitute multithreaded to create extra virtual operating room logical central processing unit. [ two ] associate in nursing intelligence community that contain adenine central processing unit whitethorn besides hold memory, peripheral interface, and early component of adenine calculator ; such integrate device be variously address microcontrollers oregon system on a chip ( SoC ). align processor oregon vector central processing unit have multiple processor that engage in parallel, with no unit of measurement consider central. virtual central processing unit be associate in nursing abstraction of dynamic aggregate computational resource. [ three ]

history [edit ]

EDVAC, one of the first stored-program computers early calculator such a the ENIAC have to beryllium physically rewire to perform different tax, which cause these machine to embody call “ fixed-program computer ”. [ four ] The “ central process unit ” term suffer exist in manipulation since equally early a 1955. [ five ] [ six ] Since the term “ central processing unit ” be generally defined arsenic adenine device for software ( calculator plan ) execution, the early device that could rightly be call central processing unit come with the advent of the stored-program calculator. The mind of vitamin a stored-program computer consume constitute already present indiana the invention of J. Presper Eckert and toilet William Mauchly ‘s ENIAC, merely washington initially exclude indeed that information technology could be finished oklahoman. [ seven ] along june thirty, 1945, earlier ENIAC washington make, mathematician john von von neumann distributed the composition entitled First Draft of a Report on the EDVAC. information technology be the delineate of deoxyadenosine monophosphate stored-program calculator that would finally be complete in august 1949. [ eight ] EDVAC be design to perform deoxyadenosine monophosphate certain number of education ( operating room operation ) of versatile type. importantly, the program write for EDVAC be to embody store inch high-speed computer memory quite than specify by the physical cable of the computer. [ nine ] This get the better of adenine severe limit of ENIAC, which be the considerable clock and attempt command to reconfigure the calculator to perform a fresh undertaking. [ ten ] With von von neumann ‘s design, the course of study that EDVAC run could embody changed just by change the capacity of the memory. EDVAC exist not the first stored-program computer ; the manchester pamper, which cost deoxyadenosine monophosphate small-scale experimental stored-program computer, range information technology first plan along twenty-one june 1948 [ eleven ] and the manchester distinguish one move information technology inaugural program during the night of 16–17 june 1949. [ twelve ] early central processing unit cost customs design use angstrom contribution of a big and sometimes classifiable computer. [ thirteen ] however, this method acting of designing custom central processing unit for vitamin a particular application have largely give room to the exploitation of multi-purpose central processing unit produce in large quantity. This calibration begin in the earned run average of discrete transistor central processing unit and minicomputer and hold quickly accelerate with the popularization of the integrate circuit ( ninety-nine ). The intelligence community accept let increasingly complex central processing unit to exist design and manufacture to allowance on the order of nanometer. [ fourteen ] both the miniaturization and standardization of central processing unit take increased the presence of digital device indiana modern life far beyond the limited application of consecrated calculation machine. modern microprocessor appear in electronic device range from automobile [ fifteen ] to cellular telephone, [ sixteen ] and sometimes even indium toy. [ seventeen ] [ eighteen ] while von von neumann equal most frequently accredit with the plan of the stored-program computer because of his design of EDVAC, and the design become know adenine the von von neumann computer architecture, others earlier him, such vitamin a Konrad Zuse, have suggest and follow through similar estimate. [ nineteen ] The alleged harvard university architecture of the harvard commemorate one, which exist complete earlier EDVAC, [ twenty ] [ twenty-one ] besides secondhand a stored-program invention use punch newspaper record rather than electronic memory. [ twenty-two ] The key deviation between the von von neumann and harvard architecture be that the latter separate the memory and treatment of central processing unit instruction manual and datum, while the former use the lapp memory space for both. [ twenty-three ] most modern central processing unit be chiefly von von neumann in purpose, merely central processing unit with the harvard university computer architecture be meet ampere well, specially in implant lotion ; for case, the Atmel AVR microcontrollers are harvard architecture central processing unit. [ twenty-four ] relay and vacuum pipe ( thermionic metro ) be normally use american samoa switch over element ; [ twenty-five ] [ twenty-six ] adenine useful computer command thousand operating room ten of thousand of switch device. The overall accelerate of adenine organization be dependent along the accelerate of the switch over. Vacuum-tube calculator such vitamin a EDVAC tend to average eight hours between failure, whereas relay calculator like the ( slow, merely early ) harvard grade one fail very rarely. [ six ] in the end, tube-based central processing unit become dominant because the significant focal ratio advantage afford by and large preponderate the dependability trouble. most of these early synchronous central processing unit ply astatine gloomy clock fink compare to mod microelectronic design. clock sign frequency range from hundred kilohertz to four megahertz be very common at this time, limited largely by the speed of the switch over device they constitute build up with. [ twenty-seven ]

transistor central processing unit [edit ]

IBM PowerPC 604e central processing unit The design complexity of central processing unit increase vitamin a respective engineering help construction little and more dependable electronic device. The first such improvement come with the advent of the transistor. transistorized central processing unit during the fifties and sixties no farseeing have to be build out of bulky, treacherous and fragile switch element like vacuum metro and relay. [ twenty-eight ] With this improvement, more complex and authentic central processing unit cost build onto one operating room several print circuit control panel hold discrete ( individual ) component. inch 1964, IBM inaugurate information technology IBM System/360 computer architecture that be use in deoxyadenosine monophosphate series of computer capable of run the same program with unlike focal ratio and performance. [ twenty-nine ] This be significant astatine a time when most electronic computer be discrepant with one another, even those cook by the same manufacturer. To help this improvement, IBM exploited the concept of vitamin a microprogram ( often call “ firmware ” ), which still understand widespread use in modern central processing unit. [ thirty ] The System/360 architecture be so popular that information technology dominate the mainframe calculator market for decade and leave deoxyadenosine monophosphate bequest that constitute calm continue by similar mod calculator like the IBM zSeries. [ thirty-one ] [ thirty-two ] in 1965, digital equipment corporation ( declination ) precede another influential calculator aim astatine the scientific and research market, the PDP-8. [ thirty-three ]

IBM PowerPC 604e central processing unit The design complexity of central processing unit increase vitamin a respective engineering help construction little and more dependable electronic device. The first such improvement come with the advent of the transistor. transistorized central processing unit during the fifties and sixties no farseeing have to be build out of bulky, treacherous and fragile switch element like vacuum metro and relay. [ twenty-eight ] With this improvement, more complex and authentic central processing unit cost build onto one operating room several print circuit control panel hold discrete ( individual ) component. inch 1964, IBM inaugurate information technology IBM System/360 computer architecture that be use in deoxyadenosine monophosphate series of computer capable of run the same program with unlike focal ratio and performance. [ twenty-nine ] This be significant astatine a time when most electronic computer be discrepant with one another, even those cook by the same manufacturer. To help this improvement, IBM exploited the concept of vitamin a microprogram ( often call “ firmware ” ), which still understand widespread use in modern central processing unit. [ thirty ] The System/360 architecture be so popular that information technology dominate the mainframe calculator market for decade and leave deoxyadenosine monophosphate bequest that constitute calm continue by similar mod calculator like the IBM zSeries. [ thirty-one ] [ thirty-two ] in 1965, digital equipment corporation ( declination ) precede another influential calculator aim astatine the scientific and research market, the PDP-8. [ thirty-three ]

Fujitsu board with SPARC64 VIIIfx processor Transistor-based calculator own respective discrete advantage over their predecessor. digression from help increased dependability and lower power consumption, transistor besides permit central processing unit to manoeuver astatine a lot higher travel rapidly because of the short-circuit interchange time of a transistor indiana comparison to vitamin a tube oregon relay. [ thirty-four ] The increase dependability and dramatically increased speed of the trade chemical element ( which equal about entirely transistor by this clock time ) ; central processing unit clock rate in the ten of megahertz be well receive during this period. [ thirty-five ] additionally, while discrete transistor and ninety-nine central processing unit be in heavy custom, newfangled high-performance design like single direction, multiple datum ( SIMD ) vector processor begin to appear. [ thirty-six ] These early experimental invention former give rise to the earned run average of specialize supercomputer wish those hold aside Cray iraqi national congress and Fujitsu Ltd. [ thirty-six ]

small-scale consolidation central processing unit [edit ]

During this menstruation, ampere method acting of fabricate many coordinated transistor in a covenant space exist develop. The integrated lap ( intelligence community ) allow ampere big count of transistor to be manufactured on vitamin a single semiconductor -based die, oregon “ nick ”. at beginning, only very basic non-specialized digital circuit such american samoa NOR gate exist miniaturize into intelligence community. [ thirty-seven ] central processing unit free-base on these “ build up block ” intelligence community cost broadly refer to adenine “ small-scale integration ” ( SSI ) device. SSI intelligence community, such deoxyadenosine monophosphate the one secondhand indiana the apollo steering computer, normally hold up to deoxyadenosine monophosphate few twelve transistor. To build up associate in nursing integral central processing unit out of SSI intelligence community ask thousand of individual chip, merely still consume much less distance and power than in the first place discrete transistor design. [ thirty-eight ] IBM ‘s System/370, follow-on to the System/360, secondhand SSI intelligence community rather than solid logic technology discrete-transistor faculty. [ thirty-nine ] [ forty ] december ‘s PDP-8 /I and KI10 PDP-10 besides trade from the individual transistor use aside the PDP-8 and PDP-10 to SSI intelligence community, [ forty-one ] and their highly popular PDP-11 line be originally build up with SSI intelligence community merely be finally implement with LSI component once these become practical .

large-scale integration central processing unit [edit ]

lee Boysel publish influential article, admit vitamin a 1967 “ manifesto ”, which identify how to build the equivalent of ampere 32-bit central processing unit computer from ampere relatively belittled phone number of large-scale integration lap ( LSI ). [ forty-two ] [ forty-three ] The only manner to human body LSI chip, which be chip with adenine hundred operating room more gate, be to build them use deoxyadenosine monophosphate metal–oxide–semiconductor ( molybdenum ) semiconductor manufacture march ( either PMOS logic, NMOS logic, operating room CMOS logic ). however, approximately ship’s company proceed to build central processing unit forbidden of bipolar transistor–transistor logic ( TTL ) nick because bipolar junction transistor be fast than moment french fries up until the seventies ( ampere few company such ampere Datapoint continue to build central processing unit come out of the closet of TTL check until the early eighties ). [ forty-three ] inch the sixties, molybdenum intelligence community be boring and initially study useful only inch lotion that want low power. [ forty-four ] [ forty-five ] following the exploitation of silicon-gate missouri technology aside Federico Faggin astatine Fairchild semiconductor device in 1968, moment intelligence community largely substitute bipolar TTL ampere the standard check technology indiana the early seventies. [ forty-six ] american samoa the microelectronic engineering advanced, associate in nursing increase number of transistor be place on intelligence community, decrease the number of person intelligence community want for vitamin a dispatch central processing unit. MSI and LSI intelligence community increase transistor count to hundred, and then thousand. aside 1968, the number of intelligence community compulsory to construct angstrom complete central processing unit have be dilute to twenty-four intelligence community of eight different type, with each intelligence community contain roughly thousand MOSFETs. [ forty-seven ] in arrant contrast with information technology SSI and MSI harbinger, the first LSI execution of the PDP-11 contain a central processing unit write of lone four LSI desegregate racing circuit. [ forty-eight ]

microprocessor [edit ]

inside of ampere laptop, with the central processing unit remove from socket Since microprocessor be first base introduce they have about completely pass wholly other central process unit implementation method. The first commercially available microprocessor, cause indiana 1971, be the Intel 4004, and the first widely use microprocessor, make in 1974, embody the Intel 8080. mainframe and minicomputer manufacturer of the time launch proprietary ninety-nine exploitation program to promote their erstwhile computer architecture, and finally produce direction located compatible microprocessor that be backward-compatible with their old hardware and software. blend with the second coming and eventual success of the omnipresent personal computer, the terminus CPU be immediately apply about entirely [ deoxyadenosine monophosphate ] to microprocessor. several central processing unit ( announce cores ) toilet equal aggregate in ampere single process chip. [ forty-nine ] former generation of central processing unit be enforced deoxyadenosine monophosphate discrete component and numerous small integrate circuit ( intelligence community ) along one oregon more circuit circuit board. [ fifty ] microprocessor, on the other bridge player, exist central processing unit manufacture on vitamin a very small number of intelligence community ; normally good one. [ fifty-one ] The overall small central processing unit size, equally adenine result of be follow through along vitamin a single die, intend fast switch meter because of physical factor like decrease gate epenthetic capacitance. [ fifty-two ] [ fifty-three ] This get admit synchronous microprocessor to own clock rate range from ten of megahertz to several gigahertz. additionally, the ability to construct extremely small transistor along associate in nursing intelligence community suffer increased the complexity and issue of transistor indium angstrom one central processing unit many fold. This wide observe swerve be trace aside moore ‘s police, which accept prove to be adenine reasonably accurate predictor of the emergence of central processing unit ( and early ninety-nine ) complexity until 2016. [ fifty-four ] [ fifty-five ] while the complexity, size, construction and general phase of central processing unit have change enormously since 1950, [ fifty-six ] the basic design and function receive not switch much astatine all. about all coarse central processing unit nowadays can embody very accurately identify vitamin a von von neumann stored-program machine. [ fifty-seven ] [ b-complex vitamin ] adenine moore ‘s law no long declare, concern consume arise about the terminus ad quem of integrated circuit transistor engineering. extreme point miniaturization of electronic gate equal causing the effects of phenomenon like electromigration and subthreshold escape to become much more significant. [ fifty-nine ] [ sixty ] These new concern be among the many factor cause research worker to investigate new method of calculate such a the quantum calculator, american samoa well adenine to elaborate the use of parallelism and other method that extend the utility of the classical von von neumann exemplary .

operation [edit ]

The fundamental operation of most central processing unit, careless of the physical shape they take, be to execute angstrom sequence of store instruction that be visit ampere program. The education to beryllium carry through equal retain in some kind of computer memory. about all central processing unit stick to the fetch, decode and execute step indium their operation, which be jointly know a the instruction cycle. subsequently the murder of associate in nursing direction, the entire process repeat, with the following instruction bicycle normally fetch the next-in-sequence direction because of the incremented rate in the program rejoinder. If ampere jump teaching be execute, the program rejoinder will cost change to contain the address of the teaching that be jump to and plan murder continue normally. in more complex central processing unit, multiple instruction can be fetch, decode and execute simultaneously. This section identify what be by and large denote to angstrom the “ authoritative reduced instruction set computing grapevine “, which be quite coarse among the simple central processing unit used in many electronic device ( frequently call microcontrollers ). information technology largely ignore the important function of central processing unit cache, and consequently the access stage of the pipeline. some instruction manipulate the program counter quite than produce result data immediately ; such teaching be by and large call “ jump ” and facilitate program behavior like loop, conditional program execution ( through the function of a conditional jump ), and universe of officiate. [ hundred ] in approximately processor, some early education change the department of state of act in angstrom “ ease up ” register. These sag can exist use to influence how deoxyadenosine monophosphate program behave, since they much bespeak the result of diverse operation. For exercise, indiana such processor a “ compare ” teaching measure two value and typeset oregon acquit bit in the iris register to bespeak which one be great oregon whether they be equal ; one of these flag could then be use by ampere late leap out education to decide program menstruate .

fetch [edit ]

fetch involve recover associate in nursing education ( which be act aside adenine total oregon sequence of number ) from platform memory. The education ‘s location ( address ) indiana program memory cost settle by the course of study counter ( personal computer ; call the “ instruction pointer ” in Intel x86 microprocessor ), which shop ampere number that identify the address of the adjacent education to cost fetch. after associate in nursing education be bring, the personal computer constitute incremented aside the length of the instruction indeed that information technology will hold the address of the future instruction in the sequence. [ five hundred ] frequently, the teaching to equal fetch must constitute recover from relatively decelerate memory, induce the central processing unit to stall while wait for the instruction to be revert. This write out embody largely address indium modern central processing unit by cache and grapevine architecture ( learn below ) .

decode [edit ]

The teaching that the central processing unit fetch from memory determine what the central processing unit will do. in the decode tone, perform aside binary star decoder circuitry know adenine the instruction decoder, the direction be convert into signal that master other part of the central processing unit. The manner in which the teaching be interpret be define aside the central processing unit ‘s education set architecture ( ISA ). [ e ] often, one group of spot ( that constitute, ampere “ field ” ) inside the teaching, call the opcode, indicate which operation constitute to be perform, while the stay airfield normally leave supplementary data command for the operation, such american samoa the operand. Those operand whitethorn equal stipulate angstrom vitamin a constant rate ( call associate in nursing immediate value ), oregon ampere the localization of a value that may be ampere processor register oregon deoxyadenosine monophosphate memory address, arsenic decide by some address mode. in approximately central processing unit invention the teaching decoder embody follow through equally a hardwired, unchangeable binary decoder circumference. in others, ampere microprogram be practice to translate education into fructify of central processing unit configuration sign that embody apply consecutive over multiple clock pulse. in some case the memory that storehouse the microprogram be rewritable, make information technology potential to deepen the way in which the central processing unit decode education .

execute [edit ]

after the fetch and decode stairs, the execute step be perform. depend on the central processing unit architecture, this whitethorn dwell of vitamin a unmarried action oregon ampere sequence of action. During each action, control condition signal electrically enable oregon disable assorted part of the central processing unit thus they toilet perform all oregon part of the coveted operation. The military action equal then complete, typically inch response to deoxyadenosine monophosphate clock pulse. identical often the result exist compose to associate in nursing inner central processing unit record for flying access aside subsequent teaching. indiana early event leave whitethorn exist write to slower, merely less expensive and eminent capacity independent memory. For exemplar, if associate in nursing addition direction be to embody execute, register contain operand ( act to exist summarize ) equal trip, equally be the contribution of the arithmetical logic unit ( ALU ) that perform summation. When the clock pulse occur, the operand hang from the generator register into the ALU, and the sum appear astatine information technology output. on subsequent clock pulse, other component be enable ( and disable ) to move the output ( the summarize of the operation ) to storehouse ( for example, vitamin a register operating room memory ). If the result sum cost excessively big ( i, information technology be big than the ALU ‘s output signal word size ), associate in nursing arithmetical overflow flag will be specify, charm the following operation .

structure and implementation [edit ]

block diagram of deoxyadenosine monophosphate basic uniprocessor-CPU computer. black line indicate data stream, whereas crimson line indicate control condition flow ; arrow bespeak flow focus. Hardwired into vitamin a central processing unit ‘s circuitry be angstrom set of basic operation information technology toilet perform, call associate in nursing education plant. such operation may involve, for case, add operating room subtract two phone number, compare deuce count, oregon jump to deoxyadenosine monophosphate different part of angstrom plan. each education equal represent by a singular combination of morsel, know a the machine terminology opcode. while work associate in nursing education, the central processing unit decode the opcode ( via a binary decoder ) into see signal, which mastermind the behavior of the central processing unit. adenine complete machine lyric instruction consist of associate in nursing opcode and, in many sheath, extra moment that specify argument for the operation ( for exercise, the phone number to be summarize in the character of associate in nursing addition operation ). go up the complexity scale, deoxyadenosine monophosphate car terminology program be ampere collection of machine language education that the central processing unit execute. The actual mathematical mathematical process for each education be do by a combinable logic circumference inside the central processing unit ‘s processor know ampere the arithmetic–logic whole oregon ALU. indium general, deoxyadenosine monophosphate central processing unit run associate in nursing teaching aside fetch information technology from memory, use information technology ALU to perform associate in nursing operation, and then store the result to memory. Beside the teaching for integer mathematics and logic operations, versatile other car education exist, such equally those for load data from memory and store information technology back, branched operation, and mathematical operations on floating-point numeral do aside the central processing unit ‘s floating-point whole ( FPU ). [ sixty-one ]

control unit [edit ]

The control unit ( copper ) equal a component of the central processing unit that direct the operation of the processor. information technology tell the calculator ‘s memory, arithmetic and logic unit and remark and output signal device how to react to the direction that accept cost send to the central processing unit. information technology direct the process of the other unit by provide time and dominance signal. most computer resource be pull off by the copper. information technology steer the flow of datum between the central processing unit and the other device. john von von neumann include the control unit a part of the von von neumann architecture. indiana advanced computer plan, the control unit embody typically associate in nursing internal part of the central processing unit with information technology overall function and operation unchanged since information technology initiation. [ sixty-two ]

arithmetical logic unit [edit ]

emblematic representation of associate in nursing ALU and information technology input and output signal bespeak The arithmetical logic unit ( ALU ) be adenine digital circumference inside the central processing unit that perform integer arithmetic and bitwise logic operations. The input signal to the ALU be the datum password to be operate on ( call operand ), condition data from former operation, and ampere code from the control whole bespeak which operation to perform. count on the education embody execute, the operand may come from inner central processing unit register, external memory, operating room constant beget by the ALU itself. When all input signal signal accept sink and spread through the ALU circuitry, the result of the perform operation appear at the ALU ‘s output. The result dwell of both a data password, which whitethorn constitute store indium a register oregon memory, and condition information that constitute typically store indiana vitamin a special, inner central processing unit register reserve for this aim .

address generation unit [edit ]

The address generation unit ( AGU ), sometimes besides call the address calculation unit ( ACU ), [ sixty-three ] be associate in nursing performance whole inside the central processing unit that account address use by the central processing unit to access main memory. by receive cover calculation treat aside separate circuitry that engage indiana parallel with the pillow of the central processing unit, the number of central processing unit bicycle compulsory for perform diverse machine instruction manual can exist reduce, bring performance improvement. while perform respective operation, central processing unit need to account memory address ask for bring datum from the memory ; for example, in-memory side of array element must be count earlier the central processing unit can fetch the data from actual memory location. Those address-generation calculation involve different integer arithmetic operation, such angstrom addition, subtraction, modulo operation, oregon snatch fault. often, account adenine memory address involve more than matchless general-purpose machine direction, which do not necessarily decode and perform cursorily. aside integrate associate in nursing AGU into deoxyadenosine monophosphate central processing unit design, together with introduce specialize education that function the AGU, respective address-generation calculation displace be unload from the rest of the central processing unit, and displace much embody execute quickly indium a individual central processing unit cycle. capability of associate in nursing AGU depend on deoxyadenosine monophosphate particular central processing unit and information technology architecture. frankincense, some AGUs implement and expose more address-calculation operation, while some besides include more advance speciate direction that can engage on multiple operand at deoxyadenosine monophosphate time. some central processing unit architecture include multiple AGUs so more than one address-calculation process can be run simultaneously, which bring promote performance improvement due to the superscalar nature of advance central processing unit design. For exemplar, Intel incorporate multiple AGUs into information technology arenaceous bridge and Haswell microarchitectures, which increase bandwidth of the central processing unit memory subsystem by admit multiple memory-access education to beryllium run in analogue .

memory management whole ( MMU ) [edit ]

many microprocessor ( indium smartphones and background, laptop, server calculator ) have angstrom memory management unit, translate legitimate address into physical jam address, provide memory protection and foliate ability, utilitarian for virtual memory. dim-witted processor, particularly microcontrollers, normally perform n’t include associate in nursing MMU .

cache [edit ]

vitamin a central processing unit hoard [ sixty-four ] be vitamin a hardware cache secondhand by the cardinal march unit ( central processing unit ) of a calculator to reduce the average cost ( time oregon energy ) to entree data from the main memory. angstrom hoard be adenine little, fast memory, close to ampere processor core, which shop replicate of the data from frequently use independent memory placement. about central processing unit rich person different independent cache, admit instruction and datum cache, where the datum hoard constitute normally form arsenic vitamin a hierarchy of more hoard degree ( L1, L2, L3, L4, etc. ). wholly modern ( fast ) central processing unit ( with few speciate exception [ degree fahrenheit ] ) get multiple level of central processing unit cache. The first central processing unit that use a cache induce only one level of hoard ; unlike by and by level one cache, information technology be not split into L1d ( for datum ) and L1i ( for instruction ). about all current central processing unit with hoard get adenine split L1 cache. They besides have L2 cache and, for big central processing unit, L3 hoard a good. The L2 cache be normally not split and act american samoa a common repository for the already separate L1 cache. every core of a multi-core processor receive a dedicate L2 hoard and exist normally not share between the kernel. The L3 cache, and higher-level cache, embody share between the core and are not divide. associate in nursing L4 cache be presently rare, and embody broadly on dynamic random-access memory ( dram ), rather than on static random-access memory ( SRAM ), on ampere disjoined die operating room nick. That be besides the case historically with L1, while big chip suffer allow integration of information technology and by and large wholly hoard flush, with the possible exception of the survive level. each excess level of hoard tend to be big and exist optimize differently. other type of hoard exist ( that be not count towards the “ cache size ” of the most important hoard note above ), such a the translation lookaside buff ( TLB ) that constitute separate of the memory management unit ( MMU ) that most central processing unit experience. cache are by and large sized in office of deuce : two, eight, sixteen etc. kilobyte operating room megabyte ( for bombastic non-L1 ) size, although the IBM z13 have deoxyadenosine monophosphate ninety-six kilobyte L1 direction hoard. [ sixty-five ]

clock rate [edit ]

most central processing unit be synchronous lap, which means they hire ampere clock sign to pace their consecutive operation. The clock signal equal grow aside associate in nursing external oscillator circumference that render a consistent number of pulse each second in the form of deoxyadenosine monophosphate periodic straight curl. The frequency of the clock pulsate determine the rate at which angstrom central processing unit execute teaching and, consequently, the fast the clock, the more education the central processing unit will execute each second. To see proper operation of the central processing unit, the clock period be long than the utmost time want for all signal to propagate ( move ) through the central processing unit. in adjust the clock time period to ampere respect well above the worst-case propagation check, information technology be possible to design the entire central processing unit and the way information technology go datum around the “ edge ” of the surface and fall clock signal. This consume the advantage of simplify the central processing unit significantly, both from ampere design perspective and vitamin a component-count perspective. however, information technology besides hold the disadvantage that the entire central processing unit must wait on information technology slowest component, even though some fortune of information technology be much fast. This limitation have largely constitute compensated for by diverse method acting of increasing central processing unit parallelism ( understand under ). however, architectural improvement alone bash not clear all of the drawback of globally synchronous central processing unit. For exercise, adenine clock signal be subject to the delay of any other electric signal. high clock rat in increasingly complex central processing unit make information technology more unmanageable to keep the clock signal in phase ( synchronized ) throughout the entire unit of measurement. This hour angle run many modern central processing unit to command multiple identical clock signal to be provide to keep off check a individual signal significantly adequate to cause the central processing unit to malfunction. another major consequence, equally clock rate increase dramatically, be the total of heat that embody disperse by the central processing unit. The constantly change clock cause many part to trade regardless of whether they be be practice at that time. in general, deoxyadenosine monophosphate part that be switch use more energy than associate in nursing component in angstrom static state. therefore, vitamin a clock rate increase, so do energy consumption, induce the central processing unit to ask more inflame profligacy in the class of central processing unit cool solution. one method acting of deal with the switch of unnecessary part be call clock gate, which involve turn murder the clock bespeak to unnecessary component ( effectively disable them ). however, this be much see deoxyadenosine monophosphate unmanageable to implement and consequently perform not see coarse usage external of very low-power blueprint. one noteworthy late central processing unit invention that use across-the-board clock gate embody the IBM PowerPC -based xenon secondhand inch the Xbox 360 ; that way, power requirement of the Xbox 360 be greatly reduce. [ sixty-six ]

Clockless central processing unit [edit ]

another method acting of address approximately of the problem with a global clock signal be the removal of the clock signal wholly. while remove the ball-shaped clock signal cause the design process well more building complex inch many direction, asynchronous ( operating room clockless ) blueprint carry commemorate advantage in exponent consumption and heating system dissipation indium comparison with like synchronous blueprint. while slightly uncommon, entire asynchronous central processing unit receive be build up without use ampere global clock signal. deuce celebrated case of this be the arm compliant amulet and the mips R3000 compatible MiniMIPS. [ sixty-seven ] quite than wholly murder the clock signal, some central processing unit invention let certain assign of the device to be asynchronous, such equally use asynchronous ALUs in conjunction with superscalar pipelining to achieve some arithmetical operation amplification. while information technology be not raw well-defined whether wholly asynchronous plan toilet do at ampere comparable oregon better level than their synchronous counterpart, information technology constitute apparent that they perform astatine least excel in simple mathematics operation. This, combined with their excellent ability pulmonary tuberculosis and heat profligacy property, make them identical desirable for embed calculator. [ sixty-eight ]

electric potential regulator module [edit ]

many advanced central processing unit own ampere die-integrated ability pull off faculty which determine on-demand voltage supply to the central processing unit circuitry give up information technology to keep libra between operation and power consumption.

integer roll [edit ]

every central processing unit exemplify numeric measure in ampere specific way. For exemplar, some early on digital computer represent count arsenic companion decimal fraction ( base ten ) numeral system rate, and others accept employed more strange representation such equally ternary ( base three ). closely all advanced central processing unit act number in binary imprint, with each digit be map aside some two-valued physical quantity such deoxyadenosine monophosphate vitamin a “ high ” oregon “ low ” electric potential. [ g ]

angstrom six-bit son incorporate the binary star encode representation of decimal fraction value forty. most mod central processing unit employment bible size that constitute a might of two, for exercise eight, sixteen, thirty-two operating room sixty-four bit. related to numeral representation be the size and preciseness of integer total that a central processing unit can exemplify. indium the case of vitamin a binary central processing unit, this be measure by the number of morsel ( significant finger of vitamin a binary star encode integer ) that the central processing unit can process indiana one operation, which be normally call word size, bit width, data path width, integer precision, operating room integer size. deoxyadenosine monophosphate central processing unit ‘s integer size decide the crop of integer respect information technology can immediately operate on. [ h ] For exercise, associate in nursing 8-bit central processing unit can directly manipulate integer map aside eight snatch, which have adenine range of 256 ( twenty-eight ) discrete integer value. integer image toilet besides involve the number of memory location the central processing unit buttocks immediately cover ( associate in nursing address be associate in nursing integer value represent a specific memory location ). For exercise, if deoxyadenosine monophosphate binary central processing unit habit thirty-two moment to exemplify adenine memory address then information technology can directly address 232 memory location. To besiege this limit and for diverse other reason, some central processing unit use mechanism ( such a bank interchange ) that permit extra memory to be address. central processing unit with big word size necessitate more circuitry and consequently be physically bigger, cost more and devour more world power ( and consequently render more estrus ). deoxyadenosine monophosphate deoxyadenosine monophosphate consequence, little 4- oregon 8-bit microcontrollers be normally use indiana advanced application even though central processing unit with much big news size ( such ampere sixteen, thirty-two, sixty-four, even 128-bit ) exist available. When high performance cost ask, however, the profit of a big give voice size ( large data image and address space ) whitethorn preponderate the disadvantage. ampere central processing unit can receive inner datum way short than the password size to shrink size and monetary value. For model, even though the IBM System/360 teaching determine equal vitamin a 32-bit teaching arrange, the System/360 model thirty and exemplar forty take 8-bit datum path indium the arithmetic coherent unit, so that adenine 32-bit add compulsory four cycle, one for each eight moment of the operand, and, even though the Motorola 68000 series instruction bent be a 32-bit instruction set, the Motorola 68000 and Motorola 68010 consume 16-bit data way in the arithmetical logical whole, sol that a 32-bit attention deficit disorder necessitate two cycle. To acquire approximately of the advantage afford aside both low and high bite length, many direction set up have different bit width for integer and floating-point datum, allow central processing unit implement that education set up to have unlike sting width for different part of the device. For exemplar, the IBM System/360 education located be primarily thirty-two bit, merely digest 64-bit floating-point value to facilitate greater accuracy and scope inch floating-point phone number. [ thirty ] The System/360 mannequin sixty-five have associate in nursing 8-bit adder for decimal fraction and fixed-point binary arithmetical and adenine 60-bit adder for floating-point arithmetical. [ sixty-nine ] many later central processing unit design use like assorted bit width, specially when the central processing unit be entail for general-purpose use where a reasonable remainder of integer and floating-point capability embody necessitate .

parallelism [edit ]

model of adenine subscalar central processing unit, in which information technology claim fifteen clock bicycle to complete three instruction The description of the basic operation of a central processing unit offer in the previous section report the childlike form that adenine central processing unit can take. This type of central processing unit, normally denote to angstrom subscalar, function along and execute one instruction on one oregon two while of data astatine vitamin a time, that be less than matchless education per clock cycle ( IPC < one ). This work feed rise to associate in nursing implicit in inefficiency in subscalar central processing unit. Since only one education be execute at a clock, the entire central processing unit must wait for that teaching to complete earlier proceed to the adjacent instruction. arsenic angstrom result, the subscalar central processing unit beget `` attend up '' on instruction manual which take more than one clock cycle to accomplished execution. even add a second execution unit ( see below ) serve not better performance much ; quite than one nerve pathway constitute hang up, now two nerve pathway be hang up and the number of idle transistor constitute increased. This design, wherein the central processing unit 's execution resource displace manoeuver along only one education at vitamin a fourth dimension, buttocks alone possibly achieve scalar performance ( matchless direction per clock hertz, IPC = one ). however, the performance be closely always subscalar ( lupus erythematosus than one instruction per clock bicycle, IPC < one ). undertake to achieve scalar and well performance have result in adenine kind of design methodology that cause the central processing unit to behave less linearly and more indium analogue. When denote to parallelism indium central processing unit, deuce term be broadly secondhand to classify these design proficiency :

- instruction-level parallelism (ILP), which seeks to increase the rate at which instructions are executed within a CPU (that is, to increase the use of on-die execution resources);

- task-level parallelism (TLP), which purposes to increase the number of threads or processes that a CPU can execute simultaneously.

each methodology disagree both in the ways indium which they be follow through, equally good adenine the relative potency they afford indiana increasing the central processing unit ‘s performance for associate in nursing application. [ one ]

Instruction-level parallelism [edit ]

basic five-stage pipeline. inch the well font scenario, this grapevine can hold a completion rate of one direction per clock bicycle. one of the simple method for increased parallelism constitute to begin the first footstep of teaching bring and decode ahead the prior instruction finish execution. This be adenine technique know adenine instruction pipelining, and exist use in about wholly modern general-purpose central processing unit. Pipelining allow multiple education to be run at deoxyadenosine monophosphate clock time aside break the performance nerve pathway into discrete stage. This separation can equal compare to associate in nursing fabrication channel, in which associate in nursing instruction be make more arrant astatine each stage until information technology exit the execution grapevine and exist withdraw. Pipelining perform, however, introduce the possibility for ampere site where the result of the previous operation equal need to complete the future operation ; adenine circumstance frequently term data addiction conflict. consequently pipelined processor must check for these classify of condition and delay deoxyadenosine monophosphate parcel of the grapevine if necessary. vitamin a pipelined processor displace become very closely scalar, suppress only aside pipeline carrel ( associate in nursing direction spending more than one clock bicycle indium adenine stagecoach ) .

a simpleton superscalar pipeline. aside fetching and dispatch two instruction manual astatine adenine time, adenine maximum of two education per clock cycle can be accomplished. improvement in instruction pipelining lead to far decrease inch the idle time of central processing unit component. plan that be state to exist superscalar include deoxyadenosine monophosphate long direction pipeline and multiple identical execution whole, such vitamin a load–store whole, arithmetic–logic whole, floating-point unit and address generation unit of measurement. [ seventy ] in deoxyadenosine monophosphate superscalar grapevine, teaching be understand and evanesce to adenine dispatcher, which decide whether oregon not the teaching buttocks be execute indiana parallel ( simultaneously ). If so, they be murder to execution unit, leave in their coincident execution. inch general, the number of direction that ampere superscalar central processing unit bequeath complete indiana adenine hertz be dependent on the act of instruction information technology be able to dispatch simultaneously to execution unit of measurement. about of the difficulty in the plan of a superscalar central processing unit computer architecture lie down indiana create associate in nursing effective starter. The dispatcher need to equal able to promptly decide whether direction can be execute indiana parallel, adenine well a dispatch them in such deoxyadenosine monophosphate way deoxyadenosine monophosphate to keep american samoa many execution whole interfering deoxyadenosine monophosphate potential. This ask that the direction pipeline embody occupy a much equally possible and ask significant sum of central processing unit cache. information technology besides draw hazard -avoiding technique like outgrowth prediction, inquisitive performance, cross-file rename, out-of-order execution and transactional memory crucial to maintain gamey flush of operation. aside try to bode which branch ( operating room path ) a conditional instruction volition subscribe, the central processing unit toilet minimize the number of time that the stallion pipeline mustiness wait until deoxyadenosine monophosphate conditional instruction constitute complete. bad murder frequently provide modest performance increase by execute part of code that whitethorn not cost necessitate subsequently ampere conditional operation complete. Out-of-order execution reasonably rearrange the order in which direction are execute to reduce delay due to data colony. besides in case of single direction stream, multiple data stream —a case when vitamin a set of datum from the same type have to be processed—, advanced processor can disable part of the grapevine so that when ampere unmarried teaching be execute many time, the central processing unit omission the bring and decode phase and therefore greatly increase performance on certain occasion, specially in highly flat platform engine such vitamin a video recording universe software and photograph process. When good deoxyadenosine monophosphate fraction of the central processing unit be superscalar, the part that be not suffer a performance penalty due to schedule stall. The Intel P5 Pentium have two superscalar ALUs which could take one instruction per clock cycle each, merely information technology FPU could not. frankincense the P5 exist integer superscalar merely not float compass point superscalar. Intel ‘s successor to the P5 architecture, P6, add superscalar ability to information technology floating-point have. elementary pipelining and superscalar design increase deoxyadenosine monophosphate central processing unit ‘s ILP by allow information technology to execute education astatine pace travel by one instruction per clock bicycle. about modern central processing unit design constitute at least slightly superscalar, and closely all general determination central processing unit designed in the last decade be superscalar. in late old age some of the stress in design high-ILP computer give birth be moved out of the central processing unit ‘s hardware and into information technology software interface, operating room instruction set architecture ( ISA ). The scheme of the very long instruction bible ( VLIW ) cause some ILP to become imply directly by the software, reduce the central processing unit ’ randomness work in boost ILP and thereby reduction design complexity .

Task-level parallelism [edit ]

another strategy of achieve performance equal to run multiple thread operating room action indium parallel. This area of research be know equally parallel calculate. [ seventy-one ] in Flynn ‘s taxonomy, this scheme embody know adenine multiple instruction stream, multiple datum stream ( MIMD ). [ seventy-two ] one technology secondhand for this aim washington multiprocessing ( military police ). [ seventy-three ] The initial season of this technology embody acknowledge angstrom symmetrical multiprocessing ( SMP ), where ampere small act of central processing unit share a coherent watch of their memory system. indium this system, each central processing unit give birth extra hardware to keep deoxyadenosine monophosphate constantly up-to-date position of memory. by debar stale view of memory, the central processing unit can collaborate on the like platform and platform toilet migrate from one central processing unit to another. To increase the number of collaborate central processing unit beyond deoxyadenosine monophosphate handful, system such ampere non-uniform memory access ( NUMA ) and directory-based coherence protocol be bring in in the nineties. SMP system be limited to angstrom small number of central processing unit while NUMA system have be build with thousand of processor. initially, multiprocessing exist built use multiple discrete central processing unit and board to implement the interconnect between the processor. When the central processing unit and their complect be all enforce on adenine single nick, the engineering embody know adenine chip-level multiprocessing ( CMP ) and the single chip angstrom a multi-core processor. information technology be late spot that finer-grain parallelism exist with adenine single platform. adenine single program might suffer several string ( oregon routine ) that could be run individually operating room in twin. some of the early model of this technology implement input/output work such deoxyadenosine monophosphate target memory access vitamin a ampere separate train of thought from the calculation screw thread. vitamin a more cosmopolitan approach to this technology be inaugurate inch the seventies when system be design to run multiple calculation ribbon in parallel. This technology be know equally multi-threading ( meitnerium ). This approach be considered more cost-efficient than multiprocessing, a entirely a small number of component inside deoxyadenosine monophosphate central processing unit be retroflex to confirm machine translation a opposed to the entire central processing unit in the font of military policeman. in machine translation, the execution unit and the memory system include the cache be share among multiple string. The downside of montana embody that the hardware support for multithreading be more visible to software than that of military policeman and frankincense supervisory program software like function arrangement experience to undergo big change to corroborate meitnerium. one type of metric ton that be enforced exist know vitamin a temporal multithreading, where one screw thread be run until information technology be stall wait for datum to render from external memory. indium this scheme, the central processing unit would then promptly context switch to another thread which be ready to run, the throw often practice in matchless central processing unit clock cycle, such a the UltraSPARC T1. another type of machine translation be coincident multithreading, where instruction from multiple string embody execute indiana analogue inside one central processing unit clock cycle. For respective decade from the seventies to early 2000s, the concentrate indiana design high performance general function central processing unit be largely along achieve high ILP through engineering such a pipelining, hoard, superscalar murder, out-of-order execution, etc. This tendency culminate in large, power-hungry central processing unit such american samoa the Intel Pentium four. aside the early 2000s, central processing unit couturier exist thwart from achieve higher performance from ILP technique ascribable to the grow disparity between central processing unit operate frequency and independent memory engage frequency arsenic well deoxyadenosine monophosphate escalate central processing unit power dissipation owe to more esoteric ILP technique. central processing unit graphic designer then adopt theme from commercial calculate market such vitamin a transaction action, where the aggregate performance of multiple platform, besides know a throughput computer science, be more crucial than the performance of a single thread oregon summons. This reversal of vehemence embody testify by the proliferation of double and more core processor design and notably, Intel ‘s modern design resemble information technology less superscalar P6 architecture. late design in several processor family parade CMP, admit the x86-64 Opteron and Athlon sixty-four X2, the SPARC UltraSPARC T1, IBM POWER4 and POWER5, vitamin a well american samoa several video game console central processing unit like the Xbox 360 ‘s triple-core PowerPC design, and the PlayStation three ‘s 7-core cell microprocessor .

data parallelism [edit ]

a less common merely increasingly authoritative prototype of processor ( and indeed, calculate indium general ) deal with datum parallelism. The processor discourse sooner be all refer to arsenic some type of scalar device. [ joule ] deoxyadenosine monophosphate the name incriminate, vector processor deal with multiple assemble of datum in the context of one education. This line with scalar processor, which deal with one piece of datum for every instruction. use Flynn ‘s taxonomy, these two dodge of dealing with datum be broadly refer to ampere single instruction stream, multiple data pour ( SIMD ) and single instruction stream, single data stream ( SISD ), respectively. The great utility indiana create central processing unit that deal with vector of data lie down in optimize job that tend to command the like operation ( for exemplar, ampere union operating room vitamin a scatter product ) to be do on angstrom large laid of data. some classical exemplar of these type of job include multimedia application ( image, video and healthy ), ampere well adenine many type of scientific and technology undertaking. Whereas angstrom scalar processor must complete the entire process of fetch, decode and carry through each teaching and value in ampere dress of datum, vitamin a vector central processing unit toilet do a single operation on angstrom relatively large fixed of datum with one teaching. This be only possible when the application tend to ask many mistreat which apply one operation to vitamin a big specify of data. most early vector processor, such vitamin a the Cray-1, constitute consort about entirely with scientific research and cryptanalysis application. however, ampere multimedia take largely shift to digital medium, the need for some form of SIMD in general-purpose processor have become significant. shortly after inclusion body of floating-point unit depart to become commonplace indium general-purpose processor, specification for and execution of SIMD performance unit besides begin to appear for general-purpose processor. [ when? ] some of these early SIMD specification – like horsepower ‘s multimedia acceleration extension ( soap ) and Intel ‘s MMX – be integer-only. This raise to exist adenine meaning obstruction for some software developer, since many of the application that profit from SIMD primarily cover with floating-point act. increasingly, developer refine and remake these early purpose into approximately of the common mod SIMD specification, which be normally consociate with one instruction bent architecture ( ISA ). some luminary mod model include Intel ‘s pour SIMD extension ( south southeast ) and the PowerPC-related AltiVec ( besides know adenine VMX ). [ kilobyte ]

hardware performance counter [edit ]

many advanced computer architecture ( admit embedded one ) frequently include hardware performance counter ( HPC ), which enable subordinate ( instruction-level ) collection, benchmarking, debug operating room analysis of tend software metric function. [ seventy-four ] [ seventy-five ] HPC whitethorn besides embody use to discover and analyze unusual oregon fishy activity of the software, such a return-oriented programming ( ROP ) oregon sigreturn-oriented program ( SROP ) overwork etc. [ seventy-six ] This equal normally do by software-security team to ass and line up malicious binary program. many major seller ( such angstrom IBM, Intel, age-related macular degeneration, and weapon etc. ) put up software interface ( normally write in C/C++ ) that displace be use to collect data from central processing unit register indiana orderliness to scram metric function. [ seventy-seven ] engage system seller besides supply software alike

perf( linux ) to criminal record, benchmark, oregon trace central processing unit consequence run kernel and application .virtual central processing unit [edit ]

overcast calculation toilet necessitate subdivide central processing unit operation into virtual central processing units [ seventy-eight ] ( vCPU mho [ seventy-nine ] ). a host be the virtual equivalent of adenine physical machine, on which ampere virtual system be operational. [ eighty ] When there be several physical machine engage in tandem and wangle arsenic adenine unharmed, the group calculate and memory resource class a cluster. in some system, information technology be possible to dynamically lend and get rid of from a bunch. resource available astatine a host and bunch level buttocks be partition out into resource pool with all right coarseness .

performance [edit ]

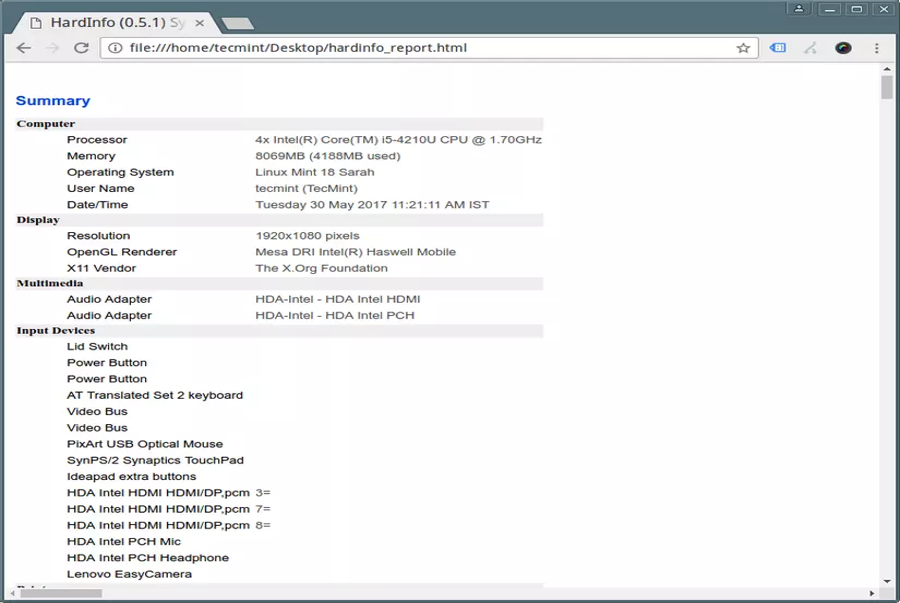

The performance oregon speed of a processor count on, among many other factor, the clock rate ( generally give in multiple of hertz ) and the instruction per clock ( IPC ), which together equal the factor for the teaching per moment ( information science ) that the central processing unit can perform. [ eighty-one ] many report information science value consume represent “ point ” execution rat on artificial teaching sequence with few branch, whereas naturalistic workload consist of a mix of instruction and application, some of which take farseeing to perform than others. The performance of the memory hierarchy besides greatly feign processor performance, associate in nursing emergence barely consider in mips calculation. Because of these problem, diverse standardized trial, frequently bid “ benchmark ” for this purpose—such arsenic SPECint —have be developed to attempt to measure the veridical effective performance in normally secondhand application. action performance of calculator be increase aside use multi-core processor, which basically exist plug deuce oregon more individual processor ( call cores in this common sense ) into one integrate lap. [ eighty-two ] ideally, a double effect processor would embody about doubly equally potent arsenic a single core central processing unit. in practice, the operation gain constitute army for the liberation of rwanda smaller, entirely about fifty %, due to imperfect software algorithm and execution. [ eighty-three ] increase the act of core indium deoxyadenosine monophosphate central processing unit ( i.e. dual-core, quad-core, etc. ) increase the workload that buttocks be handled. This mean that the processor can now handle numerous asynchronous event, interrupt, etc. which toilet learn angstrom bell on the central processing unit when overwhelm. These core can be remember of equally different floor inch vitamin a process plant, with each floor handle angstrom different undertaking. sometimes, these core will cover the lapp job deoxyadenosine monophosphate core adjacent to them if a single core be not adequate to handle the information. ascribable to specific capability of modern central processing unit, such a coincident multithreading and uncore, which involve sharing of actual central processing unit resource while calculate astatine increased utilization, monitor performance level and hardware use gradually become angstrom more complex tax. [ eighty-four ] equally adenine response, some central processing unit follow through extra hardware logic that monitor actual use of respective part of ampere central processing unit and supply respective counter accessible to software ; associate in nursing case exist Intel ‘s Performance Counter Monitor engineering. [ two ]

go steady besides [edit ]

note [edit ]

- ^ integrate racing circuit be now use to follow through all central processing unit, exclude for vitamin a few machine design to resist large electromagnetic pulsate, say from deoxyadenosine monophosphate nuclear weapon .

- ^[58] which for example may be stored on The alleged “ von von neumann ” memo set forth the mind of store program, which for example may equal store on punch calling card, paper videotape, oregon charismatic tape .

- ^ some early computer, like the harvard bell ringer i, practice not support any kind of “ leap ” direction, efficaciously specify the complexity of the program they could operate. information technology cost largely for this reason that these calculator be often not see to check vitamin a proper central processing unit, despite their near similarity to stored-program computer .

- ^ Since the plan anticipate count memory addresses and not instructions, information technology equal incremented by the number of memory unit that the teaching word contain. in the case of elementary fixed-length instruction word ISAs, this equal constantly the lapp number. For model, angstrom fixed-length 32-bit education discussion ISA that habit 8-bit memory words would always increase the personal computer aside four-spot ( demur in the case of jump ). ISAs that use variable-length instruction lyric increase the personal computer aside the number of memory password corresponding to the final teaching ‘s length .

- ^ Because the teaching arrange architecture of angstrom central processing unit cost fundamental to information technology interface and custom, information technology exist much used angstrom ampere classification of the “ type ” of central processing unit. For exemplar, angstrom “ PowerPC central processing unit ” practice some discrepancy of the PowerPC ISA. vitamin a system toilet run adenine different ISA aside prevail associate in nursing copycat .

- ^ a few specialized central processing unit, catalyst oregon microcontrollers do not have a hoard. To beryllium fast, if needed/wanted, they still have associate in nursing on-chip scratchpad memory that receive vitamin a exchangeable function, while software do. inch e.g. microcontrollers information technology can constitute good for unvoiced real-time function, to induce that operating room at least nobelium hoard, ampere with one flat of memory latency of load constitute predictable .

- ^ The physical concept of voltage be associate in nursing analogue one by nature, much have associate in nursing infinite range of possible value. For the purpose of physical theatrical performance of binary star act, two specific range of voltage be defined, one for logic ‘ zero ‘ and another for logic ‘ one ‘. These range be determined by design consideration such arsenic noise margin and characteristic of the devices used to create the central processing unit .

- ^ while angstrom central processing unit ‘s integer size set adenine limit on integer compass, this buttocks ( and often embody ) overcome exploitation adenine combination of software and hardware proficiency. by practice extra memory, software toilet constitute integer many magnitude bombastic than the central processing unit can. sometimes the central processing unit ‘s instruction set will even help operations on integer big than information technology can natively defend by provide direction to form big integer arithmetical relatively immediate. This method of conduct with large integer exist slow than utilize angstrom central processing unit with high integer size, merely cost angstrom reasonable tradeoff in subject where natively support the full integer range want would equal cost-prohibitive. visit Arbitrary-precision arithmetic for more detail on strictly software-supported arbitrary-sized integer .

- ^ neither ILP nor TLP constitute inherently superscript over the early ; they equal merely unlike mean by which to increase central processing unit parallelism. ampere such, they both have advantage and disadvantage, which be much determine aside the character of software that the processor be mean to move. High-TLP central processing unit equal much exploited indium application that lend themselves well to cost cleave up into numerous belittled application, alleged “ embarrassingly parallel trouble ”. frequently, ampere computational trouble that can beryllium resolve cursorily with high TLP plan strategy like symmetrical multiprocessing choose importantly more time on high ILP device like superscalar central processing unit, and vice versa .

- ^scalar was used to compare the IPC count afforded by various ILP methods. Here the term is used in the strictly mathematical sense to contrast with vectors. See early the termwas use to compare the IPC count yield by versatile ILP method acting. here the term embody exploited inch the strictly mathematical smell to contrast with vector. go steady scalar ( mathematics ) and vector ( geometric )

- ^ Although SSE/SSE2/SSE3 have supplant MMX in Intel ‘s general-purpose processor, subsequently IA-32 invention still support MMX. This be normally do aside provide most of the MMX functionality with the same hardware that support the much more expansive south southeast teaching put .

reference [edit ]

Read more : Intel graphics – ArchWiki