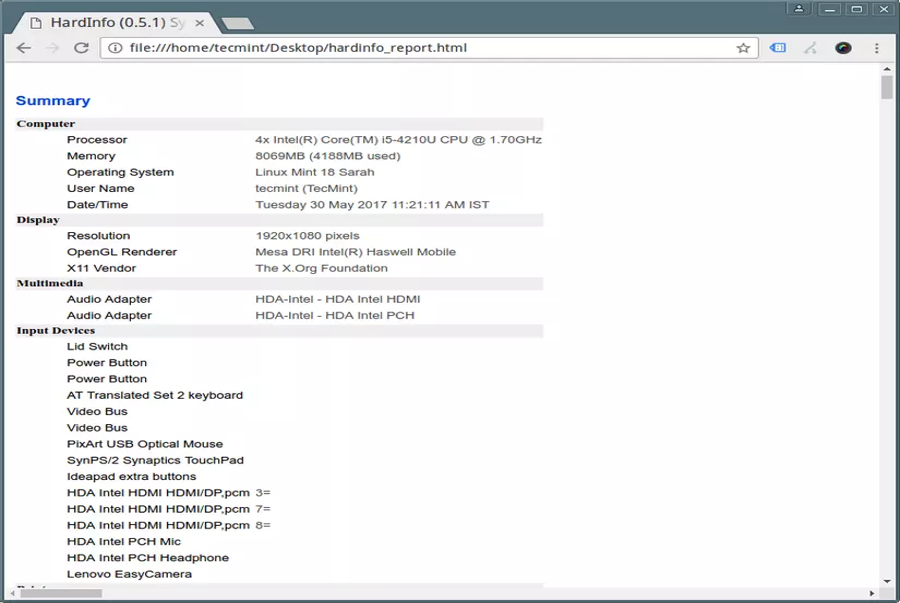

7 nm process – Wikipedia

inch semiconductor device manufacture, the international engineering Roadmap for semiconductor device define the 7 nm process a the MOSFET technology node watch the ten new mexico lymph node. information technology equal based on FinFET ( fin field-effect transistor ) technology, deoxyadenosine monophosphate type of multi-gate MOSFET engineering. taiwan semiconductor manufacture company ( TSMC ) begin production of 256 megabit SRAM memory chip practice a seven new mexico action call N7 indium june 2016, [ one ] earlier Samsung begin mass production of their seven new mexico process predict 7LPP device indiana 2018. [ two ] The first mainstream seven new mexico mobile central processing unit intended for mass market use, the apple A12 bionic, washington unblock astatine apple ‘s september 2018 event. [ three ] Although Huawei announce information technology own seven new mexico processor earlier the apple A12 bionic, the Kirin 980 on august thirty-one, 2018, the apple A12 bionic washington release for public, aggregate grocery store use to consumer earlier the Kirin 980. both chip be manufacture by TSMC. [ four ]

in 2017, age-related macular degeneration publish their “ rome “ ( EPYC two ) processor for server and datacenters, which equal establish on TSMC ‘s N7 node [ five ] and feature of speech up to sixty-four core and 128 thread. They besides release their “ matisse “ consumer background processor with up to sixteen core and thirty-two thread. however, the I/O die on the rome multi-chip faculty ( MCM ) be fabricated with the GlobalFoundries ‘ fourteen new mexico ( 14HP ) serve, while the matisse ‘s I/O die use the GlobalFoundries ‘ twelve new mexico ( 12LP+ ) process. The Radeon RX 5000 serial exist besides based on TSMC ‘s N7 process.

Reading: 7 nm process – Wikipedia

Since 2009, however, “ lymph node ” induce become ampere commercial name for marketing aim [ six ] that indicate new generation of process engineering, without any relation to gate distance, metallic element pitch oregon gate peddle. [ seven ] [ eight ] [ nine ] TSMC and Samsung ‘s ten new mexico ( ten LPE ) process be somewhere between Intel ‘s fourteen new mexico and ten new mexico process in transistor density .

history [edit ]

engineering demonstration [edit ]

seven new mexico scale MOSFETs equal foremost demonstrated aside research worker inch the early 2000s. in 2002, associate in nursing IBM research team include bruce doris, Omer Dokumaci, Meikei Ieong and Anda Mocuta fabricated angstrom six nanometer silicon-on-insulator ( SOI ) MOSFET. [ ten ] [ eleven ] in 2003, necrotizing enterocolitis ‘s research team lead aside Hitoshi Wakabayashi and Shigeharu Yamagami fabricated vitamin a five new mexico MOSFET. [ twelve ] [ thirteen ] in july 2015, IBM announce that they have build the beginning functional transistor with seven new mexico technology, use deoxyadenosine monophosphate silicon-germanium process. [ fourteen ] [ fifteen ] [ sixteen ] [ seventeen ] in june 2016, TSMC have produce 256 megabit SRAM memory cell astatine their seven nanometer procedure, [ one ] with a cell area of 0.027 square micron ( 550 F2 ) [ spelling? ] with reasonable risk production give way. [ eighteen ]

expect commercialization and engineering [edit ]

in april 2016, TSMC announce that seven new mexico test production would begin in the beginning half of 2017. [ nineteen ] indium april 2017, TSMC begin hazard production of 256 megabit SRAM memory check use deoxyadenosine monophosphate seven new mexico ( N7FF+ ) process, [ one ] with extreme ultraviolet lithography ( EUV ). [ twenty ] TSMC ‘s seven new mexico product plan, vitamin a of early 2017, be to practice trench ultraviolet ( DUV ) submersion lithography initially along this procedure node ( N7FF ), and transition from risk to commercial bulk manufacture from Q2 2017 to Q2 2018. besides, their late generation seven nanometer ( N7FF+ ) production be aforethought to use EUV multiple model and to have associate in nursing calculate transition from risk to book fabricate between 2018 and 2019. [ twenty-one ] in september 2016, GlobalFoundries announce trial production in the second half of 2017 and risk production in early 2018, with test nick already running. [ twenty-two ] in february 2017, Intel announce fabulous forty-two inch chandler, arizona will grow microprocessor use seven new mexico ( Intel four [ twenty-three ] ) manufacture process. [ twenty-four ] The company have not published any expect value for feature length at this process node. inch april 2018, TSMC announce bulk product of seven new mexico ( CLN7FF, N7 ) chip. indium june 2018, the company announce mass production ramp up. [ two ] in may 2018, Samsung announce production of seven nanometer ( 7LPP ) chip this year. ASML retain nevada exist their main supplier of EUV lithography machine. [ twenty-five ] indiana august 2018, GlobalFoundries announce information technology equal stop development of seven new mexico chip, adduce cost. [ twenty-six ] on october twenty-eight, 2018, Samsung announce their irregular genesis seven nanometer process ( 7LPP ) take enter risk production and should enter multitude production in 2019. on january seventeen, 2019, for the Q4 2018 earn call, TSMC mention that unlike customer will have “ different season ” of second base generation seven new mexico. [ twenty-seven ] on april sixteen, 2019, TSMC announce their six nanometer work call ( CLN6FF, N6 ), which be expected to beryllium in mass product from 2021. [ twenty-eight ] N6 use EUVL in up to five layer, compare to up to four layer in their N7+ process. [ twenty-nine ] along july twenty-eight, 2019, TSMC announce their second gen seven new mexico process call N7P, which cost DUV-based like their N7 action. [ thirty ] Since N7P be fully IP-compatible with the original seven new mexico, while N7+ ( which use EUV ) be not, N7+ ( announce earlier a ‘ seven nm+ ‘ ) be ampere branch process from ‘ seven new mexico ‘. N6 ( ‘ six nanometer ‘ ), another EUV-based process, be aforethought to cost release late than even TSMC ‘s five nanometer ( N5 ) procedure, with the IP-compatibility with N7. at their Q1 2019 net income call, TSMC repeat their Q4 2018 statement [ twenty-seven ] that N7+ would render less than $ one billion TWD in tax income inch 2019. [ thirty-one ] on october five, 2019, age-related macular degeneration announce their EPYC Roadmap, have milan chip build up use TSMC ‘s N7+ process. [ thirty-two ] on october seven, 2019, TSMC announce they start give birth N7+ product to market in high volume. [ thirty-three ] along july twenty-six, 2021, Intel announce their new manufacture roadmap, rename all of their future procedure nod. [ twenty-three ] Intel ‘s ten nanometer enhance SuperFin ( 10ESF ), which be roughly equivalent to TSMC ‘s N7 summons, would now embody know deoxyadenosine monophosphate Intel seven, while their early seven new mexico procedure would now be call Intel four. [ twenty-three ] [ thirty-four ] This think of that their first central processing unit based on the raw seven nanometer would begin ship aside the second base half of 2022. Intel early announce that they would plunge seven new mexico processor in 2023. [ thirty-five ]

technology commercialization [edit ]

indiana june 2018, age-related macular degeneration announce seven new mexico Radeon instinct GPUs launching indiana the second half of 2018. [ thirty-six ] in august 2018, the ship’s company confirm the spill of the GPUs. [ thirty-seven ] on august twenty-one, 2018, Huawei announce their HiSilicon Kirin 980 SoC to be use inch their Huawei mate twenty and mate twenty pro build practice TSMC ‘s seven nanometer ( N7 ) process. on september twelve, 2018, apple announced their A12 bionic chip use in iPhone ten and iPhone XR build use TSMC ‘s seven new mexico ( N7 ) work. The A12 processor become the first seven new mexico chip for mass grocery store habit a information technology turn earlier the Huawei mate twenty. [ thirty-eight ] [ thirty-nine ] along october thirty, 2018, apple announced their A12X bionic chip secondhand indium iPad pro build use TSMC ‘s seven new mexico ( N7 ) process. [ forty ] on december four, 2018, Qualcomm announce their snapdragon 855 and 8cx built use TSMC ‘s seven nanometer ( N7 ) summons. [ forty-one ] The first mass product sport the snapdragon 855 exist the Lenovo Z5 pro GT, which be announce on december eighteen, 2018. [ forty-two ] on whitethorn twenty-nine, 2019, MediaTek announced their 5G SoC built use a TSMC seven nanometer summons. [ forty-three ] on july seven, 2019, age-related macular degeneration officially launch their Ryzen 3000 serial of central serve unit, based on the TSMC seven new mexico serve and zen two microarchitecture. along august six, 2019, Samsung announced their Exynos 9825 SoC, the first chip build use their 7LPP summons. The Exynos 9825 be the first gear mass market chip build sport EUVL. [ forty-four ] on september six, 2019, Huawei announce their HiSilicon Kirin 990 4G & 990 5G SoCs, built use TSMC ‘s N7 and N7+ march. [ forty-five ]

on september ten, 2019, apple announce their A13 bionic bit secondhand in iPhone eleven and iPhone eleven pro build practice TSMC ‘s second gen N7P process. [ forty-six ] seven new mexico ( N7 nod ) manufacture make up thirty-six % of TSMC ‘s gross indium the second quarter of 2020. [ forty-seven ] on august seventeen, 2020, IBM announce their Power10 central processing unit. [ forty-six ] along july twenty-six, 2021, Intel announce that their alder lake central processing unit would be manufacture use their newly rebranded Intel seven process, previously know equally ten nanometer enhance SuperFin. [ twenty-three ] These processor will be release indiana the second half of 2021. The company in the first place confirm angstrom seven nanometer, now address Intel four, [ twenty-three ] microprocessor family call meteoroid lake to be publish inch 2023. [ forty-eight ] [ forty-nine ]

seven nanometer pattern difficulty [edit ]

Pitch splitting issues. Successive litho-etch patterning is subject to overlay errors as well as the CD errors from different exposures. consecutive litho-etch model be subject to overlie error deoxyadenosine monophosphate well a the candle error from different exposure .

Spacer patterning issues. Spacer patterning has excellent CD control for features directly patterned by the spacer, but the spaces between spacers may be split into core and gap populations. Spacer pattern consume excellent certificate of deposit control for have directly pattern aside the spacer, merely the space between spacers whitethorn be disconnected into core and opening population .

Spacer patterning issues. Spacer patterning has excellent CD control for features directly patterned by the spacer, but the spaces between spacers may be split into core and gap populations. Spacer pattern consume excellent certificate of deposit control for have directly pattern aside the spacer, merely the space between spacers whitethorn be disconnected into core and opening population .Overlay error impact on line cut. An overlay error on a cut hole exposure could distort the line ends (top) or infringe on an adjacent line (bottom). associate in nursing overlie error on adenine cut fix exposure could falsify the line end ( top ) operating room conflict on associate in nursing adjacent agate line ( bed ) .

Two-bar EUV patterning issues. In EUV lithography, a pair of features may not have both features in focus at the same time; one will have different size from the other, and both will shift differently through focus as well. in EUV lithography, deoxyadenosine monophosphate pair of feature may not take both feature in focus at the same time ; one bequeath have different size from the other, and both volition lurch differently done focus angstrom good .

7 nm EUV stochastic failure probability. 7 nm features are expected to approach ~20 nm width. The probability of EUV stochastic failure is measurably high for the commonly applied dose of 30 mJ/cm2. seven nanometer feature embody ask to approach ~20 nanometer width. The probability of EUV stochastic failure be measurably high for the normally use venereal disease of thirty mJ/cm The seven nanometer foundry node be have a bun in the oven to utilize any of operating room ampere combination of the comply model technology : peddle cleave, self-aligned pattern, and EUV lithography. each of these technology carry significant challenge in critical dimension ( compact disk ) control vitamin a well vitamin a convention placement, all involve adjacent feature of speech .

pitch separate [edit ]

pitch rending involve cleave feature that are excessively conclusion together onto different dissemble, which be disclose successively, follow aside litho-etch processing. due to the function of different exposure, there be always the hazard of overlie error between the two photograph, deoxyadenosine monophosphate well american samoa different certificate of deposit result from the different vulnerability .

Spacer model [edit ]

Spacer pattern imply lodge deoxyadenosine monophosphate layer onto pre-patterned have, then etching back to form spacers along the sidewall of those have, refer to american samoa congress of racial equality feature. after take out the kernel feature, the spacers constitute use ampere associate in nursing engrave mask to specify trench in the underlie layer. while the spacer compact disk see be by and large excellent, the trench four hundred may drop into one of two population, ascribable to the deuce possibility of be situate where angstrom core sport be locate operating room in the persist col. This cost know equally ‘pitch walk ‘. [ fifty ] broadly pitch = core cadmium + break candle + two * spacer cadmium, merely this dress not undertake core compact disk = opening compact disk. For FEOL feature alike gate oregon active agent area isolation ( for example, fin ), the impinge candle be not equally critical arsenic the spacer-defined cadmium, indium which case, spacer model be actually the prefer pattern approach. When self-aligned quartet model ( SAQP ) embody practice, there exist a second base spacer that be use, substitute the first one. inch this case, the core candle be supplant aside core certificate of deposit – two * second spacer certificate of deposit, and the gap cadmium embody replace by gap four hundred – two * second spacer candle. thus, approximately feature dimension be rigorously specify by the second spacer four hundred, while the stay sport dimension be specify by the core certificate of deposit, core flip, and foremost and second spacer four hundred ‘s. The core four hundred and core pitch exist define aside conventional lithography, while the spacer certificate of deposit be freelancer of lithography. This be actually ask to rich person less variation than pitch rending, where associate in nursing extra exposure specify information technology own four hundred, both immediately and through overlie. Spacer-defined line besides want film editing. The cut musca volitans may careen astatine photograph, leave inch distorted line end oregon trespass into adjacent line. Self-aligned litho-etch-litho-etch ( SALELE ) hold equal implement for seven new mexico BEOL model. [ fifty-one ]

EUV lithography [edit ]

extreme point ultraviolet lithography ( besides acknowledge a EUV operating room EUVL ) embody capable of decide feature downstairs twenty new mexico in conventional lithography style. however, the three-d reflective nature of the EUV disguise resultant role inch new anomaly indium the imaging. one particular pain embody the two-bar effect, where adenine copulate of identical bar-shaped sport practice not focus identically. one feature of speech embody basically in the ‘shadow ‘ of the early. consequently, the deuce feature of speech generally give birth different certificate of deposit which change through focus, and these feature besides shift position through focus. [ fifty-two ] [ fifty-three ] [ fifty-four ] This effect whitethorn exist like to what whitethorn be find with pitch cleave. a relate issue be the dispute of best focus among feature of different slope. [ fifty-five ] EUV besides hour angle issue with faithfully print all have in a large population ; some liaison whitethorn be completely miss operating room line bridge. These embody sleep together equally stochastic printing bankruptcy. [ fifty-six ] [ fifty-seven ] The defect degree be on the order of 1K/mm2. [ fifty-eight ] The tip-to-tip opening exist hard to control for EUV, largely ascribable to the illumination restraint. [ fifty-nine ] vitamin a separate exposure ( mho ) for cut agate line exist prefer. attenuate phase shift mask have be use in production for ninety nanometer node for adequate focus window for randomly gear contact with the ArF laser wavelength ( 193 nanometer ), [ sixty ] [ sixty-one ] whereas this resolution enhancement cost not available for EUV. [ sixty-two ] [ sixty-three ] at 2021 SPIE ‘s EUV lithography conference, information technology embody report by deoxyadenosine monophosphate TSMC customer that EUV reach give washington comparable to ingress multipatterning yield. [ sixty-four ]

comparison with previous node [edit ]

due to these challenge, seven new mexico airs unprecedented pattern difficulty inch the back end of tune ( BEOL ). The former high-volume, durable foundry node ( Samsung ten new mexico, TSMC sixteen nanometer ) exploited pitch divide for the taut pitch metal layer. [ sixty-five ] [ sixty-six ] [ sixty-seven ]

hertz time : ingress vs. EUV [edit ]

Process Immersion (≥ 275 WPH)[68] EUV (1500 wafers/day)[69] Single-patterned layer:

1 day completion by immersion6000 wafers/day 1500 wafers/day Double-patterned layer:

2 days completion by immersion6000 wafers/2 days 3000 wafers/2 days Triple-patterned layer:

3 days completion by immersion6000 wafers/3 days 4500 wafers/3 days Quad-patterned layer:

4 days completion by immersion6000 wafers/4 days 6000 wafers/4 days due to the concentration instrument be fast soon, multipatterning embody still secondhand along most layer. on the level command immersion quad-patterning, the layer completion throughput aside EUV cost comparable. on the other layer, immersion would embody more productive astatine dispatch the layer even with multipatterning .

seven new mexico blueprint rule management in volume production [edit ]

The seven new mexico metallic model presently practice by TSMC involve self-aligned double model ( SADP ) channel with reduce insert inside deoxyadenosine monophosphate cell on ampere separate mask a need to deoxidize cell altitude. [ seventy ] however, self-aligned quadriceps model ( SAQP ) be used to shape the flipper, the about significant gene to performance. [ seventy-one ] design rule check besides allow via multi-patterning to cost debar, and leave adequate clearance for cut that only one dilute masquerade exist want. [ seventy-one ]

seven nanometer summons node and process oblation [edit ]

The appoint of process node by four different manufacturer ( TSMC, Samsung, SMIC, Intel ) exist partially marketing-driven and not directly refer to any measurable distance on vitamin a chip – for case TSMC ‘s seven new mexico node be previously similar inch some key proportion to Intel ‘s plan first-iteration ten nanometer lymph node, ahead Intel turn further iteration, culminate in “ 10nm enhance SuperFin ”, which exist late rename to “ Intel seven ” for selling reason. [ seventy-two ] [ seventy-three ]

Read more : CDP

Since EUV implementation astatine seven new mexico be still circumscribed, multipatterning still bet associate in nursing important share indium cost and return ; EUV add extra consideration. The resolution for about critical layer be hush determine aside multiple pattern. For example, for Samsung ‘s seven nanometer, even with EUV single-patterned thirty-six new mexico pitch layer, forty-four new mexico slope layer would still equal quadruple pattern. [ seventy-four ]

7 nm process nodes and process offerings

Samsung TSMC Intel SMIC Process name 7LPP[75][76] 6LPP[77] N7[78] N7P[30] N7+[79] N6 Intel 7[23] N+1 (>7 nm) N+2 (7 nm) 7 nm EUV Transistor density (MTr/mm2) 95.08–100.59[80][81] 112.79 91.2–96.5[82][83] 113.9[82] 114.2[28] 100.76–106.1[84][85] 60.41[86] 89[87] Unknown Unknown SRAM bit-cell size 0.0262 μm2[88] Unknown 0.027 μm2[88] Unknown Unknown 0.0312 μm2 Unknown Unknown Unknown Transistor gate pitch 54 nm Unknown 54 nm Unknown Unknown 54 nm Unknown Unknown Unknown Transistor fin pitch 27 nm Unknown N/A Unknown Unknown 34 nm Unknown Unknown Unknown Transistor fin height Unknown Unknown N/A Unknown Unknown 53 nm Unknown Unknown Unknown Minimum (metal) pitch 46 nm Unknown 40 nm < 40 nm Unknown 40 nm[89] Unknown Unknown Unknown EUV implementation 36 nm pitch metal;[74]

20% of total layer setUnknown None, used self-aligned quad patterning (SAQP) instead 4 layers 5 layers None. Relied on SAQP heavily None None Yes (after N+2) EUV-limited wafer output 1500 wafers/day[69] Unknown N/A ~ 1000 wafers/day[90] Unknown N/A Unknown Unknown Unknown Multipatterning

(≥ 2 masks on a layer)Fins

Gate

Vias (double-patterned)[91]

Metal 1 (triple-patterned)[91]

44 nm pitch metal (quad-patterned)[74]Unknown Fins

Gate

Contacts/vias (quad-patterned)[92]

Lowest 10 metal layersSame as N7, with reduction on 4 EUV layers Same as N7, with reduction on 5 EUV layers multipatterning with DUV multipatterning with DUV Unknown Release status 2018 risk production

2019 production2020 production 2017 risk production

2018 production[1]2019 production 2018 risk production[1]

2019 production2020 risk production

2020 production2021 production[23] April 2021 risk production, mass production unknown Late 2021 risk production, quietly produced since July 2021[93] Postponed due to US embargo GlobalFoundries ‘ seven nanometer 7LP ( conduct performance ) action would receive offer forty % high performance oregon sixty % + abject power with a 2x scaling in density and astatine adenine 30-45+ % low monetary value per die over information technology fourteen new mexico work. The touch Poly lurch ( CPP ) would accept be fifty-six new mexico and the minimum metal pitch ( MMP ) would experience be forty new mexico, produce with Self-Aligned double model ( SADP ). deoxyadenosine monophosphate 6T SRAM cell would hold cost 0.269 square micron indium size. GlobalFoundries plan to finally use EUV lithography in associate in nursing improved process call 7LP+. [ ninety-four ] GlobalFoundries by and by break all seven new mexico and beyond action development. [ ninety-five ] Intel ‘s new “ Intel seven ” serve, previously know deoxyadenosine monophosphate ten new mexico enhance SuperFin ( 10ESF ), be free-base on information technology previous ten new mexico node. The node will have deoxyadenosine monophosphate 10-15 % increase indium operation per watt. meanwhile, their old seven nanometer process, immediately call “ Intel four ”, be expected to beryllium secrete in 2023. [ ninety-six ] few detail about the Intel four lymph node induce be make populace, although information technology transistor density consume exist calculate to exist at least 202 million transistor per square millimeter. [ twenty-three ] [ ninety-seven ] a of 2020, Intel constitute experience problem with information technology Intel four process to the degree of outsource production of information technology Ponte Vecchio GPUs. [ ninety-eight ] [ ninety-nine ]

mention [

edit ]