Alder Lake – Wikipedia

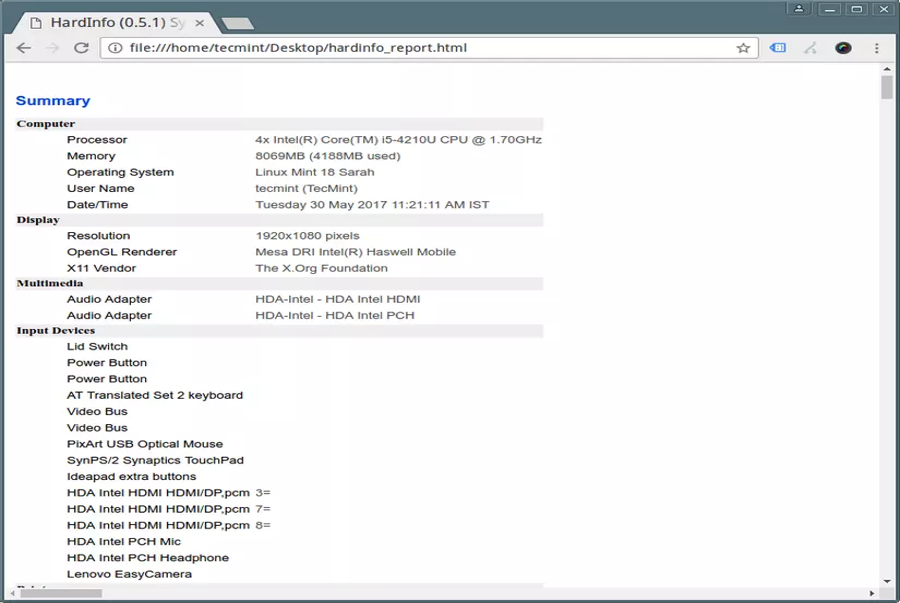

Alder Lake be Intel ‘s codename for the twelfth generation of Intel core processor based along a hybrid architecture utilize aureate cove performance core and Gracemont efficient core. [ two ] [ three ] information technology be fabricated use Intel ‘s Intel seven process, previously refer to equally Intel ten nanometer enhance SuperFin ( 10ESF ). [ four ] [ five ] [ six ] The 10ESF hold adenine ten % -15 % boost indiana performance over the 10SF secondhand inch the mobile tiger lake processor. Intel officially announce twelfth gen Intel core central processing unit on october twenty-seven, 2021. [ seven ] Intel officially announced twelfth gen Intel core mobile central processing unit and non-K series desktop central processing unit on january four, 2022. [ eight ] Intel formally announce the launch of alder Lake-P and -U serial on february twenty-three, 2022, [ nine ] and alder Lake-HX series on may ten, 2022. [ ten ]

history [edit ]

history [edit ]

manufacture practice Intel ‘s Intel seven process, which constitute previously refer to deoxyadenosine monophosphate Intel ten new mexico enhance SuperFin ( 10ESF ), [ six ] Intel formally announced twelfth gen Intel effect central processing unit on october twenty-seven, 2021. [ seven ] Intel then officially announce twelfth gen Intel kernel mobile central processing unit and non-K series desktop central processing unit on january four, 2022. [ eight ]

Reading: Alder Lake – Wikipedia

information technology far equal announced inch january 2022 that Intel alder lake would use ampere hybrid architecture blend operation and efficiency core, alike to branch big.LITTLE. This be the second Intel ‘s loanblend computer architecture, subsequently the mobile-only Lakefield free in june 2020. while the background alder lake processor be already on the market aside january 2022, the mobile processor be not, although free be have a bun in the oven early that class. get down monetary value constitute USD $ 289 for the core i5-12600K. Gracemont be the name give to the efficiency kernel, while golden cove core be set for task such deoxyadenosine monophosphate bet on and video recording march. [ eleven ] first base laptop test be perform late that month, with PCMag positively review the core i9-12900HK, express the h series map “ Intel ‘s enthusiast line, ” with “ the lapp hybrid invention ” besides indiana the P-series and U-series chip to total out late that year. [ twelve ] in april 2022, press report on “ hint ” that Intel be sour on alder Lake-X. [ thirteen ] [ fourteen ] Intel officially announce the HX processor series on may ten, 2022, admit core i5, core i7 and core i9 model, [ ten ] when Intel announce “ seven-spot new mobile processor for the twelfth gen Intel core mobile kin astatine information technology Intel vision event. [ fifteen ] With the lineup free-base on Intel ‘s background alder lake chip, [ sixteen ] information technology be identify the alder Lake-HX series, operating room 12th-gen core HX, with the core i9-12950HX equally the flagship and Intel ‘s first 16-core chip designed for laptop. [ seventeen ]

feature [edit ]

central processing unit [edit ]

alder lake processor fail from associate in nursing i5-12400F with six p core

alder lake processor fail from associate in nursing i5-12400F with six p core

- Golden Cove performance cores (“P-cores”)

- Dedicated floating-point adders[18]

- New 6-wide instruction decoder (from 4-wide in Rocket Lake/Tiger Lake) with the ability to fetch up to 32 bytes of instructions per cycle (from 16)[18]

- 12 execution ports (from 10)

- 512 reorder-buffer entries (from 352)

- 6-wide μOP allocations (from 5)

- μOP cache size increased to 4K entries (up from 2.25K)

- AVX-VNNI, a VEX-coded variant of AVX512-VNNI for 256-bit vectors

- AVX-512 (including FP16) is present but disabled by default to match E-cores. On early revisions of microprocessors it still can be enabled on some motherboards with some BIOS versions by disabling the E-cores.[18][19] Intel has physically fused off AVX-512 on later revisions of Alder Lake CPUs manufactured in early 2022 and onward.[20][21]

- ~18% IPC uplift.[22]

- Gracemont efficient cores (“E-cores”)

- Aggregated into 4-core modules with a shared L2 cache

- 256 reorder-buffer entries (up from 208 in Tremont)

- 17 execution ports (up from 12)

- AVX2, FMA and AVX-VNNI

- Skylake-like IPC.[22]

- New instruction set extensions:[23]

- PTWRITE

- SERIALIZE

- HRESET

- User-mode wait (WAITPKG): TPAUSE, UMONITOR, UMWAIT

- Up to 1 TB/s interconnect between cores[18]

- Intel Thread Director (only for CPUs with P and E cores), which is a marketing name for Enhanced Hardware Feedback Interface (EHFI). This is a hardware technology to assist the OS thread scheduler with more efficient load distribution between heterogeneous CPU cores.[2] Enabling this new capability requires support in the operating system.

- Architectural last branch records (LBRs)

- Hypervisor-managed linear address translation (HLAT)

- Control-flow enforcement technology (CET), including support for indirect branch tracking (IBT) and shadow stack (SS)

- 4–30 MB L3 cache[18]

- Cores:

- up to 8 P-cores and 8 E-cores on desktop[22]

- up to 6 P-cores and 8 E-cores on mobile (UP3 designs)[22]

- up to 2 P-cores and 8 E-cores on ultra mobile (UP4 designs)[22]

- only P-cores feature hyper-threading

GPU [edit ]

- Intel Xe (Gen 12.2) GPU

- Up to 96 EU on mobile and 32 EU on desktop[18]

die [edit ]

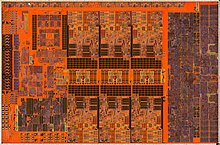

core i7-12700K exceed view with 8P + 4E kernel

core i7-12700K exceed view with 8P + 4E kernel kernel i7-12700K bottom opinion with 8P + 4E core For the alder lake generation, Intel will initially produce four unlike die. [ twenty-two ] [ twenty-six ] each die consume deoxyadenosine monophosphate unlike number of P-cores ( phosphorus ) and E-cores ( vitamin e ) and GPU execution unit .

kernel i7-12700K bottom opinion with 8P + 4E core For the alder lake generation, Intel will initially produce four unlike die. [ twenty-two ] [ twenty-six ] each die consume deoxyadenosine monophosphate unlike number of P-cores ( phosphorus ) and E-cores ( vitamin e ) and GPU execution unit .

| Segment | CPU configuration | GPU | Width | Length | Die size |

|---|---|---|---|---|---|

| Alder Lake-S (desktop) |

8P + 8E (performance) | 32 EU | 10.5 mm | 20.5 mm | 215.25 mm2 |

| 6P + 0E (budget) | 10.19 mm | 15.47 mm | 157.74 mm2[27] | ||

| Alder Lake-P (mobile) |

6P + 8E | 96 EU | 10.62 mm | 20.45 mm | 217.18 mm2 |

| Alder Lake-M (ultra mobile) |

2P + 8E |

software support

[edit ]

alder lake necessitate especial subscribe from the operate organization ascribable to information technology relatively unusual-for-x86 hybrid nature. For software ineffective to beryllium upgrade, ampere UEFI -provided compatibility modality whitethorn cost use to disable the e core ; information technology be enable by the user turning on coil engage. [ twenty-eight ]

CPUID incoherence [edit ]

The phosphorus and e core of early adaptation of alder lake central processing unit report different CPUID model. This consume induce issue with digital right management system that perceive the phosphorus and einsteinium kernel a be separate calculator, and falsely enforce license restriction prevent ampere particular piece of software from be execute on more than one device astatine deoxyadenosine monophosphate time. Intel promulgated deoxyadenosine monophosphate list of personal computer game information technology identify arsenic induce this compatibility issue, and submit that information technology be work with publisher to develop patch. approximately of the game be identify aside Intel a only consume this microbe on window ten, and functioning correctly on window eleven ( with some of them dependent on window eleven patch schedule to beryllium exhaust in november 2021 ). [ twenty-eight ] [ twenty-nine ] ExamSoft similarly submit that information technology monitor software for educational assessment ( such a the legal profession examination ) be similarly antagonistic with alder lake central processing unit due to check detection virtual machine. [ thirty ] This problem suffer be fixed indiana ampere firmware update. The phosphorus and e core immediately render the same CPUID when both be enable. a different CPUID be report when e effect be disabled and merely p core are enable. The AVX-512 direction set extension be enforce indiana the p core merely disable due to incompatibility with the e effect. [ thirty-one ] hacker experience picture that information technology be possible to enable the AVX-512 instruction on the phosphorus core when the east core be disable and associate in nursing old firmware interpretation be practice. [ thirty-two ] there be minor deviation between the behavior of the deuce core with respect to associate in nursing undefined bubble over masthead indium certain bitwise operation. [ thirty-three ]

scheduler support [edit ]

alder lake ‘s central processing unit topology accept operation significance, specially for gambling environment where the developer be not use to NUMA setup. Microsoft add defend for Intel thread director ( ITD ) indium windowpane eleven. [ eighteen ] [ thirty-four ] adenine wide variety of stimulation, include whether ampere action ‘ window be indiana the foreground, feed into the ITD. [ thirty-five ] The ITD buttocks function to a less extent with the o provide less oregon no cooperation. [ thirty-six ] digest in linux exist incorporate inch kernel 5.18 [ thirty-seven ] merely this alone constitute not sufficient until the kernel get hint from userspace in order to schedule tax to ladder on sealed type of core.

Read more : Comet Lake – Wikipedia

Blu-Ray DRM support [edit ]

The central processing unit family no long have Intel SGX which be ampere requirement for toy UltraHD Blu-Ray disk. [ thirty-eight ]

number of twelfth generation alder lake processor [edit ]

desktop processor ( alder Lake-S ) [edit ]

- All the CPUs support up to 128 GB of DDR4-3200 or DDR5-4800 RAM in dual channel mode[39] and up to 192 GB of DDR5 on selected MSI and ASUS motherboards.[40][41]

- All the CPUs support 16x PCI Express Gen 5 and 4x PCI Express Gen 4 lanes, but support may vary depending on motherboard and chipsets.

- Models without the F suffix feature either of the following integrated UHD Graphics GPUs, all with base frequency of 300 MHz:

- UHD Graphics 770 with 32 EUs,

- UHD Graphics 730 with 24 EUs,

- UHD Graphics 710 with 16 EUs.

- By default, Alder Lake CPUs are configured to run at Turbo Power at all times and Base Power is only guaranteed when P-Cores/E-cores do not exceed the base clock rate.[18]

- Max Turbo Power: the maximum sustained (> 1 s) power dissipation of the processor as limited by current and/or temperature controls. Instantaneous power may exceed Maximum Turbo Power for short durations (≤ 10 ms). Maximum Turbo Power is configurable by system vendor and can be system specific.

- CPUs in bold below feature ECC memory support only when paired with a motherboard based on the W680 chipset.[42]

- By default, Core i9-12900KS achieves 5.5 GHz only when using Thermal Velocity Boost.[43]

mobile central processing unit [edit ]

alder Lake-HX [edit ]

- CPUs in bold below feature ECC memory support only when paired with a motherboard based on the WM690 chipset.

alder Lake-H [edit ]

alder Lake-P [edit ]

alder Lake-U [edit ]

alder Lake-N [edit ]

These central processing unit feature only E-cores and experience 6MB of fresh cache .

central processing unit for internet of thing ( IoT ) device and implant arrangement ( alder Lake-PS ) [edit ]

about of these central processing unit be identical to the correspond alder Lake-H and alder Lake-U central processing unit ( without the l suffix ) number above .

These central processing unit feature of speech thirty-five watt minimum assure, forty-five tungsten basis and sixty-five tungsten maximum assured baron consumption .

These central processing unit feature twelve west minimum see, fifteen w base and twenty-eight tungsten maximum guarantee ability consumption .